AD9520-1BCPZ-REEL7;AD9520-1BCPZ;AD9520-1PCBZ;中文规格书,Datasheet资料

12 LVPECL/24 CMOS Output Clock

Generator with Integrated 2.5 GHz VCO

AD9520-1 Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 https://www.sodocs.net/doc/216292871.html, Fax: 781.461.3113 ?2008 Analog Devices, Inc. All rights reserved.

FEATURES

Low phase noise, phase-locked loop (PLL)

On-chip VCO tunes from 2.27 GHz to 2.65 GHz

Supports external 3.3 V/5 V VCO/VCXO to 2.4 GHz

1 differential or

2 single-ended reference inputs

Accepts CMOS, LVDS, or LVPECL references to 250 MHz Accepts 16.67 MHz to 33.3 MHz crystal for reference input Optional reference clock doubler

Reference monitoring capability

Auto and manual reference switchover/holdover modes,

with selectable revertive/nonrevertive switching Glitch-free switchover between references

Automatic recovery from holdover

Digital or analog lock detect, selectable

Optional zero delay operation

Twelve 1.6 GHz LVPECL outputs divided into 4 groups

Each group of 3 has a 1-to-32 divider with phase delay Additive output jitter as low as 225 fs rms

Channel-to-channel skew grouped outputs <16 ps

Each LVPECL output can be configured as 2 CMOS outputs (for f OUT ≤ 250 MHz)

Automatic synchronization of all outputs on power-up Manual synchronization of outputs as needed

SPI- and I2C-compatible serial control port

64-lead LFCSP

Nonvolatile EEPROM stores configuration settings APPLICATIONS

Low jitter, low phase noise clock distribution

Clock generation and translation for SONET, 10Ge, 10G FC, and other 10 Gbps protocols

Forward error correction (G.710)

Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceivers

ATE and high performance instrumentation

Broadband infrastructures

GENERAL DESCRIPTION

The AD9520-11 provides a multioutput clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 2.27 GHz to 2.65 GHz. An external 3.3 V/5 V VCO/VCXO of up to 2.4 GHz can also be used.

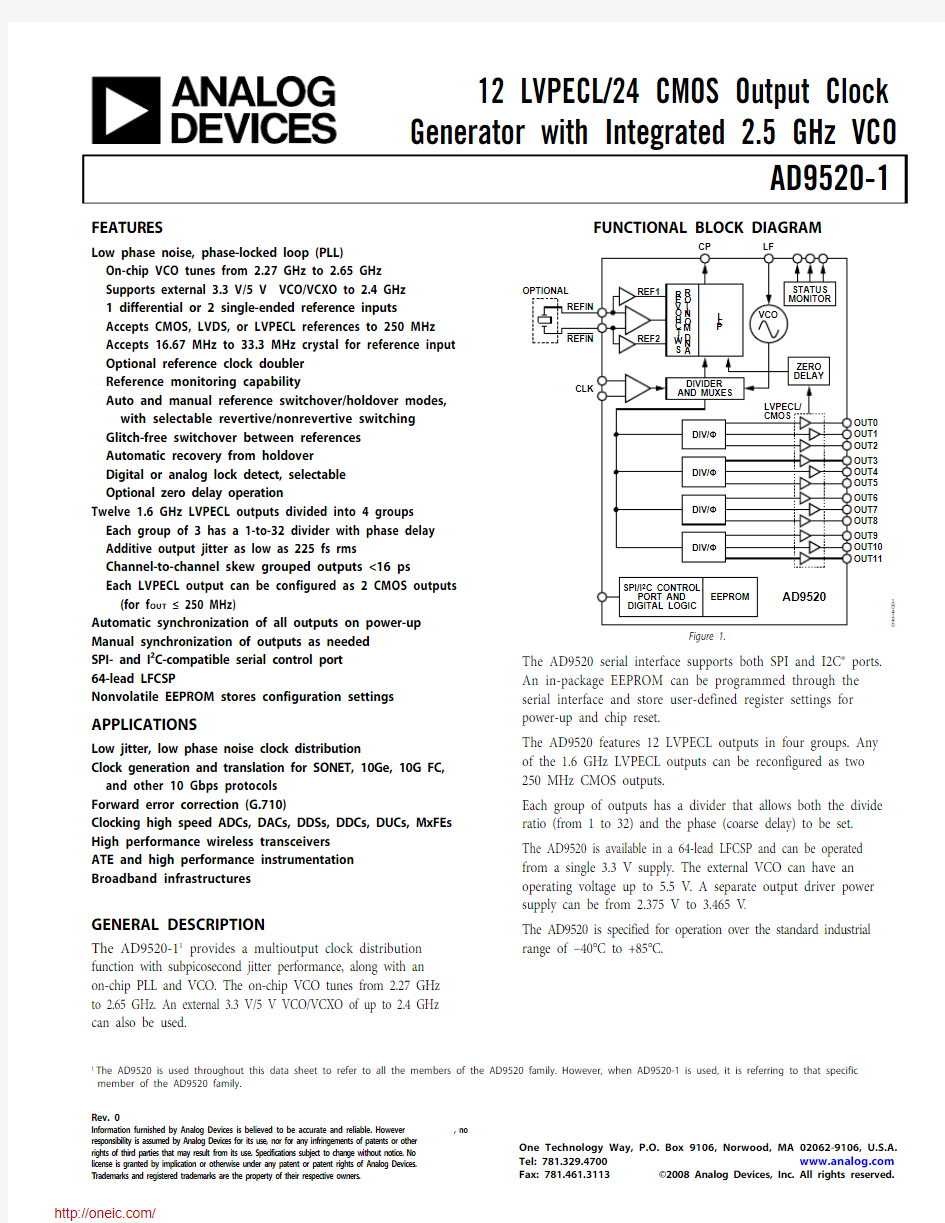

FUNCTIONAL BLOCK DIAGRAM

7

2

1

4

-

1

Figure 1.

The AD9520 serial interface supports both SPI and I2C? ports. An in-package EEPROM can be programmed through the serial interface and store user-defined register settings for power-up and chip reset.

The AD9520 features 12 LVPECL outputs in four groups. Any of the 1.6 GHz LVPECL outputs can be reconfigured as two 250 MHz CMOS outputs.

Each group of outputs has a divider that allows both the divide ratio (from 1 to 32) and the phase (coarse delay) to be set. The AD9520 is available in a 64-lead LFCSP and can be operated from a single 3.3 V supply. The external VCO can have an operating voltage up to 5.5 V. A separate output driver power supply can be from 2.375 V to 3.465 V.

The AD9520 is specified for operation over the standard industrial range of ?40°C to +85°C.

1 The AD9520 is used throughout this data sheet to refer to all the members of the AD9520 family. However, when AD9520-1 is used, it is referring to that specific member of the AD9520 family.

AD9520-1

Rev. 0 | Page 2 of 84

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications ....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 3 Specifications ..................................................................................... 4 Power Supply Requirements ....................................................... 4 PLL Characteristics ...................................................................... 4 Clock Inputs .................................................................................. 7 Clock Outputs ............................................................................... 7 Timing Characteristics ................................................................ 8 Timing Diagrams ..................................................................... 9 Clock Output Additive Phase Noise (Distribution Only;

VCO Divider Not Used) ............................................................ 10 Clock Output Absolute Phase Noise (Internal VCO Used) .. 11 Clock Output Absolute Time Jitter (Clock Generation

Using Internal VCO) .................................................................. 11 Clock Output Absolute Time Jitter (Clock Cleanup

Using Internal VCO) .................................................................. 11 Clock Output Absolute Time Jitter (Clock Generation

Using External VCXO) .............................................................. 12 Clock Output Additive Time Jitter

(VCO Divider Not Used) .......................................................... 12 Clock Output Additive Time Jitter (VCO Divider Used) ..... 13 Serial Control Port—SPI Mode ................................................ 13 Serial Control Port—I2C Mode ................................................ 14 PD , SYNC , and RESET Pins ..................................................... 15 Serial Port Setup Pins: SP1, SP0 ............................................... 15 LD, STATUS, and REFMON Pins ............................................ 15 Power Dissipation ....................................................................... 16 Absolute Maximum Ratings .......................................................... 17 Thermal Resistance .................................................................... 17 ESD Caution ................................................................................ 17 Pin Configuration and Function Descriptions ........................... 18 Typical Performance Characteristics ........................................... 21 Terminology .................................................................................... 26 Detailed Block Diagram . (27)

Theory of Operation ...................................................................... 28 Operational Configurations ...................................................... 28 Mode 0: Internal VCO and Clock Distribution ................. 28 Mode 1: Clock Distribution or External

VCO < 1600 MHz .................................................................. 30 Mode 2: High Frequency Clock Distribution—CLK or

External VCO > 1600 MHz .................................................. 32 Phase-Locked Loop (PLL) .................................................... 34 Configuration of the PLL ...................................................... 34 Phase Frequency Detector (PFD) ........................................ 34 Charge Pump (CP) ................................................................. 35 On-Chip VCO ........................................................................ 35 PLL External Loop Filter ....................................................... 35 PLL Reference Inputs ............................................................. 35 Reference Switchover ............................................................. 36 Reference Divider R ............................................................... 36 VCO/VCXO Feedback Divider N: P , A, B, R ..................... 36 Digital Lock Detect (DLD) ................................................... 38 Analog Lock Detect (ALD) ................................................... 38 Current Source Digital Lock Detect (CSDLD) .................. 38 External VCXO/VCO Clock Input (CLK/CLK ) ................ 39 Holdover .................................................................................. 39 External/Manual Holdover Mode ........................................ 39 Automatic/Internal Holdover Mode .................................... 39 Frequency Status Monitors ................................................... 41 VCO Calibration .................................................................... 42 Zero Delay Operation ................................................................ 43 Internal Zero Delay Mode ..................................................... 43 External Zero Delay Mode .................................................... 43 Clock Distribution ..................................................................... 44 Operation Modes ................................................................... 44 CLK or VCO Direct-to-LVPECL Outputs .......................... 44 Clock Frequency Division ..................................................... 45 VCO Divider ........................................................................... 45 Channel Dividers ................................................................... 45 Synchronizing the Outputs—SYNC Function ................... 47 LVPECL Output Drivers ....................................................... 49 CMOS Output Drivers . (49)

AD9520-1

Rev. 0 | Page 3 of 84

Reset Modes (49)

Power-On Reset ....................................................................... 49 Hardware Reset via the RESET Pin ...................................... 49 Soft Reset via the Serial Port.................................................. 50 Soft Reset to Settings in EEPROM when

EEPROM Pin = 0 via the Serial Port (50)

Power-Down Modes ................................................................... 50 Chip Power-Down via PD ..................................................... 50 PLL Power-Down .................................................................... 50 Distribution Power-Down ..................................................... 50 Individual Clock Output Power-Down ................................ 50 Individual Clock Channel Power-Down ............................. 50 Serial Control Port .......................................................................... 51 SPI/I2C Port Selection ................................................................ 51 I2C Serial Port Operation ........................................................... 51 I 2C Bus Characteristics ........................................................... 51 Data Transfer Process ............................................................. 52 Data Transfer Format ............................................................. 53 I2C Serial Port Timing ............................................................ 53 SPI Serial Port Operation ........................................................... 54 Pin Descriptions ...................................................................... 54 SPI Mode Operation ............................................................... 54 Communication Cycle—Instruction Plus Data .................. 54 Write ......................................................................................... 54 Read .......................................................................................... 54 SPI Instruction Word (16 Bits) .................................................. 55 SPI MSB/LSB First Transfers ..................................................... 55 EEPROM Operations ..................................................................... 58 Writing to the EEPROM ............................................................ 58 Reading from the EEPROM ...................................................... 58 Programming the EEPROM Buffer Segment.......................... 59 Register Section Definition Group ....................................... 59 IO_UPDATE (Operational Code 0x80) .............................. 59 End-of-Data (Operational Code 0xFF) ............................... 59 Pseudo-End-of-Data (Operational Code 0xFE) ................. 59 Thermal Performance ..................................................................... 61 Register Map .................................................................................... 62 Register Map Descriptions ............................................................. 67 Applications Information ............................................................... 82 Frequency Planning Using the AD9520 .................................. 82 Using the AD9520 Outputs for ADC Clock Applications .... 82 LVPECL Clock Distribution ...................................................... 82 CMOS Clock Distribution ......................................................... 83 Outline Dimensions ........................................................................ 84 Ordering Guide (84)

REVISION HISTORY

9/08—Revision 0: Initial Version

AD9520-1

SPECIFICATIONS

Typical (typ) is given for VS = VS_DRV = 3.3 V ± 5%; VS ≤ VCP ≤ 5.25 V; T A = 25°C; RSET = 4.12 kΩ; CPRSET = 5.1 kΩ, unless otherwise noted. Minimum (min) and maximum (max) values are given over full VS and T A (?40°C to +85°C) variation.

POWER SUPPLY REQUIREMENTS

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

VS 3.135 3.3 3.465 V 3.3 V ± 5%

VS_DRV 2.375 VS V This is nominally 2.5 V to 3.3 V ± 5%

VCP VS 5.25 V This is nominally 3.3 V to 5.0 V ± 5%

RSET Pin Resistor 4.12 kΩ Sets internal biasing currents; connect to ground

CPRSET Pin Resistor 5.1 kΩ Sets internal CP current range, nominally 4.8 mA (CP_lsb = 600 μA);

actual current can be calculated by CP_lsb = 3.06/CPRSET; connect to ground BYPASS Pin Capacitor 220 nF Bypass for internal LDO regulator; necessary for LDO stability; connect to ground

PLL CHARACTERISTICS

Rev. 0 | Page 4 of 84

AD9520-1

Rev. 0 | Page 5 of 84

Parameter Min Typ Max Unit Test Conditions/Comments Crystal Oscillator Crystal Resonator Frequency Range 16.67 33.33 MHz Maximum Crystal Motional Resistance 30 Ω PHASE/FREQUENCY DETECTOR (PFD) PFD Input Frequency 100 MHz Antibacklash pulse width = 1.3 ns, 2.9 ns 45 MHz Antibacklash pulse width = 6.0 ns Reference Input Clock Doubler Frequency 0.004 50 MHz Antibacklash pulse width = 1.3 ns, 2.9 ns Antibacklash Pulse Width 1.3 ns 0x017[1:0] = 01b 2.9 ns 0x017[1:0] = 00b; 0x017[1:0] = 11b 6.0 ns 0x017[1:0] = 10b CHARGE PUMP (CP) I CP Sink/Source Programmable High Value 4.8 mA With CPRSET = 5.1 kΩ; higher I CP is possible by

changing CPRSET

Low Value 0.60 mA With CPRSET = 5.1 kΩ; lower I CP is possible by

changing CPRSET

Absolute Accuracy 2.5 % Charge pump voltage set to V CP /2 CPRSET Range 2.7 10 kΩ I CP High Impedance Mode Leakage 1 nA Sink-and-Source Current Matching 1 % 0.5 V < V CP < VCP ? 0.5 V; V CP is the voltage on the CP (charge

pump) pin; VCP is the voltage on the VCP power supply pin

I CP vs. V CP 1.5 % 0.5 V < V CP < VCP ? 0.5 V I CP vs. Temperature 2 % V CP = VCP/2 V PRESCALER (PART OF N DIVIDER) Prescaler Input Frequency P = 1 FD 300 MHz P = 2 FD 600 MHz P = 3 FD 900 MHz P = 2 DM (2/3) 600 MHz P = 4 DM (4/5) 1000 MHz P = 8 DM (8/9) 2400 MHz P = 16 DM (16/17) 3000 MHz P = 32 DM (32/33) 3000 MHz Prescaler Output Frequency 300 MHz A, B counter input frequency (prescaler input frequency

divided by P)

PLL N DIVIDER DELAY Register 0x019[2:0]; see Table 53000 Off 001 410 ps 010 530 ps 011 650 ps 100 770 ps 101 890 ps 110 1010 ps 111 1130 ps PLL R DIVIDER DELAY Register 0x019[5:3]; see Table 53000 Off 001 370 ps 010 490 ps 011 610 ps 100 730 ps 101 850 ps 110 970 ps 111 1090 ps

AD9520-1

1 The REFIN and REFIN self-bias points are offset slightly to avoid chatter on an open input condition.

2 For reliable operation of the digital lock detect, the period of the PFD frequency must be greater than the unlock-after-lock time.

Rev. 0 | Page 6 of 84

AD9520-1 CLOCK INPUTS

1 Below about 1 MHz, the input should be dc-coupled. Care should be taken to match V CM.

CLOCK OUTPUTS

Rev. 0 | Page 7 of 84

AD9520-1

Rev. 0 | Page 8 of 84

TIMING CHARACTERISTICS

Table 5.

Parameter Min Typ Max Unit Test Conditions/Comments LVPECL OUTPUT RISE/FALL TIMES Termination = 50 Ω to VS_DRV ? 2 V Output Rise Time, t RP 130 170 ps 20% to 80%, measured differentially (rise/fall

times are independent of VS and are valid for VS_DRV = 3.3 V and 2.5 V)

Output Fall Time, t FP 130 170 ps 80% to 20%, measured differentially (rise/fall

times are independent of VS and are valid for VS_DRV = 3.3 V and 2.5 V)

PROPAGATION DELAY, t PECL , CLK-TO-LVPECL OUTPUT For All Divide Values 850 1050 1280 ps High frequency clock distribution configuration 800 970 1180 ps Clock distribution configuration Variation with Temperature 1.0 ps/°C

OUTPUT SKEW, LVPECL OUTPUTS 1

Termination = 50 Ω to VS_DRV ? 2 V LVPECL Outputs That Share the Same Divider 5 16 ps VS_DRV = 3.3 V 5 20 ps VS_DRV = 2.5 V LVPECL Outputs on Different Dividers 5 45 ps VS_DRV = 3.3 V 5 60 ps VS_DRV = 2.5 V All LVPECL Outputs Across Multiple Parts 190 ps VS_DRV = 3.3 V and 2.5 V CMOS OUTPUT RISE/FALL TIMES Termination = open Output Rise Time, t RC 750 960 ps 20% to 80%; C LOAD = 10 pF; VS_DRV = 3.3 V Output Fall Time, t FC 715 890 ps 80% to 20%; C LOAD = 10 pF; VS_DRV = 3.3 V Output Rise Time, t RC 965 1280 ps 20% to 80%; C LOAD = 10 pF; VS_DRV = 2.5 V Output Fall Time, t FC 890 1100 ps 80% to 20%; C LOAD = 10 pF; VS_DRV = 2.5 V PROPAGATION DELAY, t CMOS , CLK-TO-CMOS OUTPUT Clock distribution configuration For All Divide Values 2.1 2.75 3.55 ns VS_DRV = 3.3 V 3.35 ns VS_DRV = 2.5 V Variation with Temperature 2 ps/°C VS_DRV = 3.3 V and 2.5 V

OUTPUT SKEW, CMOS OUTPUTS 1

CMOS Outputs That Share the Same Divider 7 85 ps VS_DRV = 3.3 V 10 105 ps VS_DRV = 2.5 V All CMOS Outputs on Different Dividers 10 240 ps VS_DRV = 3.3 V 10 285 ps VS_DRV = 2.5 V All CMOS Outputs Across Multiple Parts 600 ps VS_DRV = 3.3 V 620 ps VS_DRV = 2.5 V

OUTPUT SKEW, LVPECL-TO-CMOS OUTPUT 1

All settings identical; different logic type Outputs That Share the Same Divider 1.18 1.76 2.48 ns LVPECL to CMOS on same part Outputs That Are on Different Dividers 1.20 1.78 2.50 ns LVPECL to CMOS on same part

1

The output skew is the difference between any two similar delay paths while operating at the same voltage and temperature.

AD9520-1

Rev. 0 | Page 9 of 84

Timing Diagrams

CLK

07214-060

Figure 2. CLK/CLK to Clock Output Timing, Div = 1

07214-061

Figure 3. LVPECL Timing, Differential

07214-063

Figure 4. CMOS Timing, Single-Ended, 10 pF Load

AD9520-1

Rev. 0 | Page 10 of 84

CLOCK OUTPUT ADDITIVE PHASE NOISE (DISTRIBUTION ONLY; VCO DIVIDER NOT USED)

Table 6.

Parameter Min Typ Max Unit Test Conditions/Comments CLK-TO-LVPECL ADDITIVE PHASE NOISE Distribution section only; does not include

PLL and VCO

CLK = 1 GHz, Output = 1 GHz Input slew rate > 1 V/ns Divider = 1 @ 10 Hz Offset ?107 dBc/Hz @ 100 Hz Offset ?117 dBc/Hz @ 1 kHz Offset ?127 dBc/Hz @ 10 kHz Offset ?135 dBc/Hz @ 100 kHz Offset ?142 dBc/Hz @ 1 MHz Offset ?145 dBc/Hz @ 10 MHz Offset ?147 dBc/Hz @ 100 MHz Offset ?150 dBc/Hz CLK = 1 GHz, Output = 200 MHz Input slew rate > 1 V/ns Divider = 5 @ 10 Hz Offset ?122 dBc/Hz @ 100 Hz Offset ?132 dBc/Hz @ 1 kHz Offset ?143 dBc/Hz @ 10 kHz Offset ?150 dBc/Hz @ 100 kHz Offset ?156 dBc/Hz @ 1 MHz Offset ?157 dBc/Hz >10 MHz Offset ?157 dBc/Hz CLK-TO-CMOS ADDITIVE PHASE NOISE Distribution section only; does not include

PLL and VCO

CLK = 1 GHz, Output = 250 MHz Input slew rate > 1 V/ns Divider = 4 @ 10 Hz Offset ?107 dBc/Hz @ 100 Hz Offset ?119 dBc/Hz @ 1 kHz Offset ?125 dBc/Hz @ 10 kHz Offset ?134 dBc/Hz @ 100 kHz Offset ?144 dBc/Hz @ 1 MHz Offset ?148 dBc/Hz >10 MHz Offset ?154 dBc/Hz CLK = 1 GHz, Output = 50 MHz Input slew rate > 1 V/ns Divider = 20 @ 10 Hz Offset ?126 dBc/Hz @ 100 Hz Offset ?133 dBc/Hz @ 1 kHz Offset ?140 dBc/Hz @ 10 kHz Offset ?148 dBc/Hz @ 100 kHz Offset ?157 dBc/Hz @ 1 MHz Offset ?160 dBc/Hz >10 MHz Offset ?163 dBc/Hz

分销商库存信息:

ANALOG-DEVICES

AD9520-1BCPZ-REEL7AD9520-1BCPZ AD9520-1/PCBZ

综合布线题目汇总

单元一认识综合布线工程 1、填空题 (1)综合布线系统就就是用数据与通信电缆、光缆、各种软电缆及有关连接硬件构成的通用布线系统,它能支持语音、数据、影像与其她控制信息技术的标准应用系统。 (2)综合布线系统就是集成网络系统的基础,它能满足数据,语音及视频图像等的传输要求,就是智能大厦的实现基础。 (3)在GB 50311-2007《综合布线系统工程设计规范》国家标准中规定,在智能建筑工程设计中宜将综合布线系统分为基本型、增强型、综合型三种常用形式。 (4)综合布线系统包括7个子系统,分别就是工作区子系统,水平子系统,垂直子系统,管理间子系统,设备间子系统与建筑群子系统,进线间子系统。 (5)在工作区子系统中,从RJ45插座到计算机等终端设备间的跳线一般采用双绞线电缆,长度不宜超过5米。 (6)安装在墙上或柱上的信息插座应距离地面30厘米以上。 (7)水平子系统主要由信息插座,配线架,跳线等组成。 (8)水平子系统通常由 4 对非屏蔽双绞线组成,如果有磁场干扰时可用屏蔽双绞线。 (9)垂直子系统负责连接管理间子系统到设备间子系统,实现主配线架与中间配线架的连接。(10)管理间子系统就是连接垂直子系统与水平干线子系统的设备,其配线对数由管理的信息点数来决定。 2.选择题(部分为多选题) (1)GB50311-2007《综合布线系统工程设计规范》中,将综合布线系统分为几个子系统。( C ) A 5 B 6 C 7 D 8 (2)工作区子系统又称为服务区子系统,它就是由跳线与信息插座所连接的设备组成。其中信息插座包括以下哪些类型?( ABC ) A墙面型 B地面型 C桌面型 D吸顶型 (3)常用的网络终端设备包括哪些? ( ABD ) A计算机 B电话机与传真机 C汽车 D 报警探头与摄像机 (4)设备间入口门采用外开双扇门,门宽一般不应小于多少米?(B ) A 2米 B 1、5米 C 1米 D 0、9米 (5)在网络综合布线工程中,大量使用网络配线架,常用标准配线架有哪些?( BD ) A 18口配线架 B 24口配线架 C 40口配线架 D 48口配线架 (6)为了减少电磁干扰,信息插座与电源插座的距离应大于多少毫米?(C ) A 100毫米 B 150毫米 C 200毫米 D 500毫米 (7)按照GB 50311国家标准规定,铜缆双绞线电缆的信道长度不超过多少米?( C ) A 50米 B 90米 C 100米 D 150米 (8)按照GB 50311国家标准规定,水平双绞线电缆最长不宜超过多少米?(B ) A 50米 B 90米 C 100米 D 150米 (9)总工程师办公室有下列哪些信息化需求?(ABC ) A 语音 B数据 C 视频 D 用餐。 (10)在水平子系统的设计中,一般要遵循以下哪些原则?(ABC ) A 性价比最高原则 B 预埋管原则 C水平缆线最短原则 D 使用光缆原则 3、思考题 (1)在工作区子系统的设计中,一般要遵循哪些原则? (2)水平子系统中双绞线电缆的长度为什么要限制在90米以内? (3)管理间子系统的布线设计原则有哪些? (4)GB 50311-2007《综合布线系统工程设计规范》国家标准第7、0、9条为强制性条文, 必须严格执行。请问该条就是如何规定的?为什么这样规定? (5)请绘制出设备间子系统的原理图。

苹果电脑快捷键大全

一、开机时按下…… 滑鼠按键弹出抽取式媒介(2.4f1版以前的Boot ROM可能不包括退出CD片) Option键在配备「New World」韧体系统的机种上叫出「Open Firmware」开机系统选择功能。 苹果键+Option键按住这两个键,直到电脑发出二次声响,就会改以Mac OS 9开机。 苹果键+x(有时只按住x键)如果Mac OS 9和Mac OS X在同一个开机用的硬碟区段(partition)上,按这个键会强迫以OS X开机。 苹果键+Option+shift+delete 跳过原定的启动磁碟,改以外接磁碟(或光碟机)开机。 这个按键的主要作用,其实是强迫电脑不要从预设的启动磁碟读入系统档案,所以会产生从其他磁碟开机的「副作用」。如果您的Mac是配备SCSI介面的机种,它会从编号(ID)最高的磁碟机往下搜寻,直到找出可以开机的磁碟区段为止。至於在配备IDE 介面的机种上则不确定它的搜寻顺序。 苹果键+Option+shift+delete+# 从指定ID的SCSI磁碟开?#代表SCSI编号)。 苹果键+Option+p+r 清除系统参数记忆体(PRAM),必须按住不放,等发出两次响声之后再放开。 苹果键+Option+n+v 清除NV RAM,类似在Open Firmware中做「重置全部」(reset+all)的动作。 苹果键+Option+o+f 开机时进入open firmware。 苹果键+Option+t+v 强制Quadra AV机种使用外接电视机当作显示器。 苹果键+Option+x+o 以唯读记忆体中所烧录的系统软体开机(仅适用於Mac Classic 机种)。 苹果键+Option+a+v 强制电脑辨识苹果AV显示器。 c 使用光碟开机。如果原先设定由OS X开机,但光碟机里没有放置开机光碟,则可能 会改由OS 9开机。 d 强制以内建磁碟机开机。 n 按住n键直到萤幕上出现Mac标志,电脑会尝试透过BOOTP或TFTP以网路伺服器开机。 r 强制PowerBook重置萤幕设定。 t 强制配备FireWire介面的机种进入外接磁碟模式(FireWire Target Disk mode)。 shift 关闭所有延伸功能(OS 9或OS X之下的Classic环境)。 shift 关闭登入项目,同时也会关闭所有不必要的程式核心(kernel)延伸功能(也就是所谓安全开机模式,仅适用OS X 10.1.3或更新的系统版本)。 苹果键开机时关闭虚拟记忆体(Virtual Memory,仅适用OS 9或OS X之下的Classic 环境)。 空白键开机时启动延伸功能管理程式(OS 9或OS X之下的Classic环境)。 苹果键+v 开机过程中显示控制台讯息(仅适用OS X)。 苹果键+s 开机后进入单一使用者模式(仅适用OS X)。 苹果键+Option+c+i 先将系统时钟设定为日期1989年9月20日,然后以这个按键组合开机,就可以看到萤幕上显示特殊的系统小秘密(仅适用於Mac IIci机种)。 苹果键+Option+f+x 先将系统时钟设定为日期1990年3月19日,然后以这个按键组合开机,就可以看到萤幕上显示特殊的系统小秘密(仅适用於Mac IIfx机种)。 二、萤幕上出现小Mac笑脸时按下……

SAI绘图软件快捷键大全

SAI绘图软件快捷键大全、SAI常用快捷键 sai是绘制漫画常用的工具,掌握好快捷键的使用,会让你事倍功半,sai画布旋转快捷键,其实就是ALT+空格然后鼠标左键按住旋转。。。 SAI绘图软件快捷键大全 钢笔工具的↓(我钢笔工具很少用,就这些吧……,搜的) ctrl 在钢笔图层中激活锚点状态,以加锚点的方式调整线条的曲线,也可直接选择锚点进行挑战。 ctrl+拖拉锚点锚点移动。 shift 不加锚点的调整,(注意:按ctrl的是加锚点的调整,除非你点在某个锚点上。) ctrl+shift 复制并移动整个线条的所有锚点。

alt+shift 单纯只移动整个线条的所有锚点。 ctrl+shift 焊接两个锚点,连接线条时非常有用,如两个锚点分别属于两条线条,则自动连接。 alt 删除锚点。 ctrl+alt 笔刷大小调整。 alt+space 旋转画布。 tab 全屏切換 快捷键 space:移动画布 ALT+space:旋转画布 ALT:取色 TAB:全屏显示画布 CTRL+E:向下合并图层(不过我觉得那个向下合并图像的功能比较好用。还会自己帮你开一个图层) CTRL+F:填充 CTRL:移动图层 SHIFT:画直线用的 CTRL+D:取消选区 CTRL:钢笔图层中按住CTRL可以随意移动、增加描点 ALT+CTRL:调整画笔大小

特殊的键操作: 方向键滚动视图 空格+左键拖拽滚动视图 CTRL+左键拖拽移动图层、移动选择部分 CTRL+SHIFT+左键拖拽选择图层并移动 CTRL+空格+左键拖拽视图的变焦框 CTRL+空格+左键单击放大视图 CTRL+空格+右键单击重置视图的放大 CTRL+ALT+空格+左键拖拽视图的变焦框 CTRL+ALT+空格+左键单击缩小视图 CTRL+ALT+空格+右键单击重置视图的缩小 ALT+空格+左键拖拽旋转视图 ALT+空格+右键单击重置视图的旋转 [ 选择小一号的笔刷 ] 选择大一号的笔刷 0~9 选择笔刷浓度 - 切换透明色与前景色 X 切换前景色和背景色 笔刷类工具的键操作: SHIFT+左键拖拽开始将最后描画的位置和拖拽的开始点连接成直线CTRL+ALT+左键拖拽更改笔刷尺寸 ALT+左键单击拾色

综合布线总结

第一单元智能建筑和综合布线 (1)智能建筑的定义:将结构、系统、服务、运营、及相关关系全面综合并达到最优化组合,以获得高效率、高性能与高舒适性的大楼或建筑。智能建筑有三部分构成:建筑自动化或楼宇自动化(Building automation,BA)、通信自动化(communication automation,CA)和办公自动化(office automation,OA)。(2)综合布线系统(GCS)是智能建筑得以实现的高速公路,综合布线是衡量智能化建筑的智能化程度的重要标志。 (3)建筑与建筑群综合布线系统(Premises Distribution system , PDS),经我国国家标准GB/T 50311—2000命名的综合布线系统(Generic Cabling System , GCS). (4)综合布线的特点:①兼容性,所谓兼容性是指其设备或程序可以用在多种系统中的特性、②开放性:对于传统的布线方式,用户选定了某种设备,也就选定了与之相适应的布线方式和传输介质。③灵活性:在综合布线系统中,由于所有信息系统皆采用相同的传输介质和物理星状拓扑结构,因此所有的信息通道都是通用的。④可靠性:综合布线系统采用高品质的材料和组合压接的方式构成一套高标准的信息通道。⑤先进性:综合布线系统通常采用光缆与双绞线电缆混合布线方式,这种方式能够十分合理地构成一套完整的布线系统。⑥经济性:衡量一个建筑产品的经济性,应该从两个方面加以考虑,即初期投资和性能/价格比。 (5)综合布线系统一般采用分层星状拓扑结构。 (6)综合布线系统工程宜按下列七个部分进行设计:①工作区②配线子系统③干线子系统④建筑群子系统⑤设备间⑥进线间⑦管理 第二单元,网络传输介质与连接器件 (1)按美国线缆标准(American Wire Gauge ,AWG),双绞线的绝缘铜导线线芯大小有22、24和26等规格,常用的5类和超5类非屏蔽双绞线是24AWG,直径约为0.51mm,规格数字越大,导线越细。加上绝缘层的铜导线直径约为 0.92mm。典型的加上塑料外部护套的超5类非屏蔽双绞线电缆直径约为5.3mm。 (2)UTP非屏蔽双绞线电缆的优点为:①无屏蔽外套,直径小,节省所占用的空间②质量小、易弯曲、易安装③将串扰减至最小或加以消除④具有阻燃性。 (3)5类D级电缆最高频率带宽为100MHz,传输速率为100Mbps(可达100Mbps),主要应用与语音、100Mbps的快速以太网,最大网段长为100m,采用RJ链接器,用于数据通信的5类产品已淡出市场。㈠超5类双绞线---CAT 5e:超5类/D级双绞线(Enhanced CAT 5)或称为“5类增强型”、“增强型5类”,简称5e类。 (4)T568A:白绿—绿、白橙—蓝、白蓝—橙、白棕—棕。 T568B:白橙—橙、白绿—蓝、白蓝—绿、白棕—棕。 (5)光纤有一下几个优点:①光纤通信的频带很宽,理论可达30亿兆赫【兹】②电磁绝缘性能好。③衰减较小,在较大范围内基本上是一个常数值④需要增设光中继器的间隔距离较大,因此整个通道中中继器的数目可以减少,降低成本 ⑤重量轻,体积小,适用的环境温度范围宽,使用寿命长。⑥光纤通信不带电,使用安全,可用于易燃易爆场所。⑦ 抗化学腐蚀能力强,适用于一些特殊环境下的布线。㈡光纤也存在着一些缺点:如质地脆,机械强度低;切断和连接中技术要求较高等。 (6)光纤的分类⑴按材料成分可分为:玻璃光纤、胶套硅光纤和塑料光纤⑵按传输模式可分为:单模光纤和多模光纤。(7)光缆的分类:①按敷设方式分有架空光缆、管道光缆、铠装地理光缆、水底光缆和海底光缆等。②按光缆结构分有束管式光缆,层绞式光缆,紧抱式光缆,带式光缆,非金属光缆和可分支光缆等。③按用途分有长途通信用光缆,短途室外光缆、室内光缆和混合光缆等。 第三单元产品选型` (1)满足功能需求 (2)结合环境实际 (3)选用同一品牌的产品 (4)符合相关标准 (5)技术性与经济性相结合 第四单元综合布线系统设计 (1)信息模块材料预算方式如下:m=n+n*3% 式中的:m---信息模块的总需求量;n---信息点的总量;n*3%-----裕量

macbook pro 键盘快捷键

macbook pro键盘快捷键 系统启动 在启动时按下X: 强制使用Mac OS X启动电脑 在启动时按下Option-Command-Shift-Delete: 不使用主要启动硬盘,并寻找使用外接磁盘与CD 在启动时按下C: 由具有系统文件夹的CD光盘启动 在启动时按下N: 试图由兼容的网络服务器(NetBoot)启动 在启动时按下T: 以火线目标磁盘方式启动 在启动时按下Shift: Mac OS X 10.2后,在「安全启动状态」启动,一切启动项目及不必要运行的核心扩展文件皆不运行 在启动时按下Command-V: 以Verbose状态启动,将临时进入UNIX界面,短时不可使用鼠标 在启动时按下Command-S: 以单一用户状态启动,将进入UNIX界面,不可使用鼠标Finder窗口 Command-W:

关闭窗口 Option-Command-W: 关闭一切窗口 Command-右方向箭头: 在列表中扩展文件夹内容 Option-Command-右方向箭头: 在列表中扩展此文件夹及一切下属文件夹内容 Command-左方向箭头: 在列表中缩闭文件夹内容 Option-Command-上方向箭头: 打开所述文件夹,并关闭现在窗口 菜单指令 Shift-Command-Q (苹果菜单): 登出用户 Shift-Option-Command-Q (苹果菜单): 立即登出用户 Shift-Command-Delete (Finder菜单): 倾倒废纸篓 Option-Shift-Command-Delete (Finder菜单): 倾倒废纸篓,而不需要经由确认对话框确定Command-H (Finder菜单): 菜单隐藏Finder

网络综合布线总结报告

网络综合布线技术竞赛项目竣工总结报告 一、项目名称: 网络综合布线技术竞赛项目。 二、设计施工依据: GB50311-2007《综合布线系统工程设计规范》 GB50312-2007《综合布线系统工程验收规范》 三、项目概括: 利用大赛组委会提供的1套网络综合实训装置、2套网络配线实训装置等综合布线实训器材。通过安装模拟三层墙的工作区子系统、水平布线子系统、管理间子系统、垂直子系统的安装,管理间与设备间的连接,设备间的建筑群的连接,以及线缆的端接与测试。完全模拟了工程实际的TO→CD的情况,完成项目的设计、安装、调试、竣工资料编写。 四、施工步骤: 1.项目组分工 项目组工三人,一人主要负责设计项目,同时完成复杂永久链路的端接;一人负责模拟墙线管与线槽的安装;另一人负责管理间、设备间、建筑群子系统配线架的安装与线缆的端接。 2.施工过程: 根据项目要求完成施工图、系统图、信息点点数统计表、端口对应表等设计内容,完成竣工资料编写。 完成工作区子系统的信息点18个底盒、25个信息模块安装与端接;水平系统的线管与线槽的安装,线缆的敷设;完成管理间、设备间、建筑群子系统的机柜配线架的安装与线缆端接的任务。并进行万县的制作、复杂永久链路的端接、模块端接和线缆测试。 五、收获与体会: 在技术方面我们通过对项目的实施,加深了对GB50311-2007《综合布线系统工程设计规范》、GB50312-2007《综合布线系统工程验收规范》的学习与理解。 在思想品质方面,通过团队配合与协作,增强了组织管理、协调、表达沟通的能力,培养了吃苦耐劳、克服困难的意志品质。 总之,通过本项目的实施,增强了我们实践经验和动手能力,为我们将来“零”距离就业做好了充分的准备。

(完整版)MAC版PS快捷键

MAC版PS快捷键 Command + A 全选 Command + D 取消选择 Shift + Command + D 恢复选择 Command + X 剪切 Command + C 复制 Command + V 粘贴 Command + Ctrl + I 反选 Command + T 自由变换 Shift + Command + T 重复上一步的变换和程度 Alt + Command + D 羽化调节 Command + L 水平调节 Command + M 曲线调节 Command + B 色彩平衡调节 Command + U 色饱和度 调节 Shift + Command + U 图象变黑白 Command + E 向下合并图层 Shift + Ctrl + E 合并可见图层 Command + 0 满画布显示 Command + + 放大显示 Command + -缩小显示 Command + 鼠标左健图象移动工具 空格键+ 鼠标左健手形工具 Tab 隐藏、显示控制面板 Esc 取消 F1 帮助 工具箱(多种工具共用一个快捷键的可同时按【Shift】加此快捷键选取)矩形、椭圆选框工具【M】 裁剪工具【C】 移动工具【V】 套索、多边形套索、磁性套索【L】 魔棒工具【W】 喷枪工具【J】 画笔工具【B】 像皮图章、图案图章【S】 历史记录画笔工具【Y】 像皮擦工具【E】

铅笔、直线工具【N】 模糊、锐化、涂抹工具【R】 减淡、加深、海棉工具【O】 钢笔、自由钢笔、磁性钢笔【P】 添加锚点工具【+】 删除锚点工具【-】 直接选取工具【A】 文字、文字蒙板、直排文字、直排文字蒙板【T】 度量工具【U】 直线渐变、径向渐变、对称渐变、角度渐变、菱形渐变【G】 油漆桶工具【K】 吸管、颜色取样器【I】 抓手工具【H】 缩放工具【Z】 默认前景色和背景色【D】 切换前景色和背景色【X】 切换标准模式和快速蒙板模式【Q】 标准屏幕模式、带有菜单栏的全屏模式、全屏模式【F】 临时使用移动工具【Command】 临时使用吸色工具【Alt】 临时使用抓手工具【空格】 打开工具选项面板【Enter】 快速输入工具选项(当前工具选项面板中至少有一个可调节数字) 【0】至【9】循环选择画笔【[】或【]】 选择第一个画笔【Shift】+【[】 选择最后一个画笔【Shift】+【]】 建立新渐变(在”渐变编辑器”中) 【Command】+【N】 文件操作 新建图形文件【Command】+【N】 用默认设置创建新文件【Command】+【Alt】+【N】 打开已有的图像【Command】+【O】 打开为... 【Command】+【Alt】+【O】 关闭当前图像【Command】+【W】 保存当前图像【Command】+【S】 另存为... 【Command】+【Shift】+【S】 存储副本【Command】+【Alt】+【S】 页面设置【Command】+【Shift】+【P】 打印【Command】+【P】 打开“预置”对话框【Ctrl】+【K】 显示最后一次显示的“预置”对话框【Alt】+【Command】+【K】 设置“常规”选项(在预置对话框中) 【Command】+【1】 设置“存储文件”(在预置对话框中) 【Command】+【2】

SAI好用快捷键大全

E:一直按住E,笔会变成橡皮,松开就变回笔。按一下就是橡皮,不知这样说是否清楚。。N:铅笔 V:笔 B:喷枪 C:水彩笔 D:清除 还有一些,我不是很常用,画画的习惯不同,如果你常用,也记一下吧。 A:选择笔 H:翻转画布 S:选区擦 X:背景颜色和前景颜色转换 F:将选区的图合并到下一图层,是转写,ctrl+E是向下合并 还有一些常用的(这些不说大家应该也知道): Delete:左旋转画布(逆时针) End:右旋转画布(顺时针) Alt+空格+鼠标左键:旋转画布 Alt+空格+鼠标右键:恢复旋转画布(按Home也可以) Ctrl++:放大 Ctrl+-:放小 Ctrl+0:恢复视图视窗大小 Ctrl+空格+鼠标左键:局部放大(这个比较常用吧,想放大哪就放大哪,放多大也好控制)空格+鼠标左键:移动画布 Ctrl+T:自由变换 空格+鼠标左键:任意移动画布 】:大一号的笔刷 【:小一号的笔刷 0~9:选择笔刷浓度 Ctrl+Alt+鼠标左键:(左右拖动)调整笔刷大小 Alt+鼠标左键:拾色 Ctrl+Z:撤销 用虚线选择选区时,按住Ctrl是移动,按住Alt是减区域,按住Shift是加区域。 画直线:用笔点一个点,按住Shift,再点一个点,两个点之间就会形成一条直线。 钢笔工具的↓ ctrl:在钢笔图层中激活锚点状态,以加锚点的方式调整线条的曲线,也可直接选择锚点进

行挑战。 ctrl+拖拉锚点:锚点移动。 shift :不加锚点的调整,(注意:按ctrl的是加锚点的调整,除非你点在某个锚点上。)ctrl+shift:复制并移动整个线条的所有锚点。 alt+shift:单纯只移动整个线条的所有锚点。 ctrl+shift :焊接两个锚点,连接线条时非常有用,如两个锚点分别属于两条线条,则自动连接。 alt :删除锚点。 SAI快捷键; ctrl;在钢笔图层中激活锚点状态,以加锚点的方式调整线条的曲线,也可直接选择锚点进行挑战。 ctrl+拖拉锚点,锚点移动。 shift ;不加锚点的调整,(注意:按ctrl的是加锚点的调整,除非你点在某个锚点上。) ctrl+shift ;复制并移动整个线条的所有锚点。 alt+shift ;单纯只移动整个线条的所有锚点。 ctrl+shift ;焊接两个锚点,连接线条时非常有用,如两个锚点分别属于两条线条,则自动连接。 alt ;删除锚点。 ctrl+alt ;笔刷大小调整。 alt+space ;旋转画布。 tab ;全屏切换。 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++ +++++++++++++++++ 特殊的键操作: 方向键;滚动视图。

综合布线总结与心得

综合布线总结与心得 这次关于综合布线的实训持续了两周多,从最初的方案设计,到后来的综合布线,小组成员相互合作,最终完成了这次实训。虽然我们小组没有中标,但在实训的过程中每个人都做好了自己的工作,也让我学到了很多新的知识。 综合布线是一种模块化的、灵活性极高的建筑物内或建筑群之间的信息传输通道。它既能使语音、数据、图像设备和交换设备与其它信息管理系统彼此相连,也能使这些设备与外部相连接。它还包括建筑物外部网络或电信线路的连接点与应用系统设备之间的所有线缆及相关的连接部件。综合布线系统由不同系列和规格的部件组成,其中包括:传输介质、相关连接硬件(如配线架、连接器、插座、插头、适配器)以及电气保护设备等。这些部件可用来构建各种子系统,它们都有各自的具体用途。 综合布线系统大致可以分为七个部分,分别是:工作区;配线子系统;干线子系统;建筑群子系统;设备间;进线间与管理。 实际上布线工作中要遵循一定的规律,此规律不仅体现于结构化布线工程实施所要遵循的相关规范和标准,还需要符合在工程中摸索出来的许多经验和教训。综合布线作为已经成熟的行业,在经历了大量实践的基础上积累了许多可以借鉴的实用经验。布线过程管理混乱、工艺落后、技术陈旧,都会给施工单位本身带来工程质量、成本和进度上的不足。使用先进规范的施工操作规程是企业取得效益和立足市场的必由之路。 一、工程应用综合布线工程一般步骤为:调研—方案设计—土建施工—技术安装—信息点测试—文档整理—维护。 (1)调研:主要任务是询问客户网络需求,现场勘察建筑,根据建筑平面图等资料

去结算线材的用量,信息插座的数目和机柜定位、数量,做出综合布线调研报告; (2)布线方案设计:根据前期勘察数据做出布线材料预算表、工程进度安排表; (3)土建施工:协调施工队与业主进行职责商谈,提出布线许可,主要是钻孔、走线、信息插座定位、机柜定位、做线标识;(4)技术安装:主要是打信息模块,打配线架、机柜内部安装;(5)信息点测试:一般测试,采用12点测试仪,单人可以进行,效率较高,主要测试通断情况,可打印出详细的测试报告; (6)文档管理:最终要提供交给客户的峻工报告(材料实际用量表、测试报告、楼层(楼群)配线表,为日后维护提供数据依据; (7)维护:当线路出现故障时,快速进行响应。 二、技术 1、PVC管槽施工过程时,一定要把线先划好,如果不预先画划好线直接施工很容易造成PVC走线不水平或垂直,虽然这样前期工作花时间较多,但方便以后PVC装钉。 2、打室外通到室内墙孔时,要注意先量好准确的位置,然后才分别从两边钻孔,先用小钻定位,再用中钻打通,再改大钻加大孔径,这样可避免打裂墙面。 3、拉线。这一环节十分重要,如果决策或测量有误,将造成不可挽回的损失。 4、打信息模块时,有一点非常要注意:由于特殊原因,打模块时外皮离模块大约要有1CM,因为这类模块较长,不照上面做的话,装好的模块那防尘板会难移动,失去弹性,所以都要这样做才能确保模块安装的合理。 三、经验

Mac快捷键大全

Mac快捷键大全 您可以按组合键来实现通常需要鼠标、触控板或其他输入设备才能完成的操作。 要使用键盘快捷键,请按住一个或多个修饰键,同时按快捷键的最后一个键。例如,要使用快捷键Command-C(拷贝),请按住Command 键并按C 键,然后同时松开这两个键。Mac 菜单和键盘通常使用某些按键的符号,其中包括以下修饰键: 如果您使用的是Windows PC 专用键盘,请用Alt 键代替Option 键,用Windows 标志键代替Command 键。有些Mac 键盘在顶行中设有特殊按键,快捷键中也会用到它们;这些按键上有音量图标、显示屏亮度图标和其他功能图标。按下图标键可执行相应功能,将其与Fn 键组合可用作F1、F2、F3 或其他标准功能键。 要了解更多快捷键,请查看您所用应用的菜单。每个应用都有自己的快捷键,在一个应用中有用的快捷键可能不能用于另一个应用。 剪切、拷贝、粘贴和其他常用快捷键

睡眠、注销和关机快捷键 按下可打开Mac 电源或将Mac 从睡眠状态唤醒。 当Mac 处于唤醒状态时,按住这个按钮1.5 秒钟会 显示一个对话框,询问您是要睡眠、重新启动还是关 机。如果您不想等待1.5 秒钟,请按下Control–电 源按钮或Control–介质推出键。* 按住这个按钮5 秒钟会强制Mac 关机。 Control–Shift–电源按钮或 Control–Shift–介质推出键 将显示器置于睡眠状态。 Control–Command–介质推出键退出所有应用,然后重新启动 文稿有未存储的更改,系统将询问您要不要存储这些更改。

质推出键 *不适用于带有 Multi-Touch Bar 的键盘。文稿快捷键

综合布线题目汇总

综合布线题目汇总 Prepared on 22 November 2020

单元一认识综合布线工程 1.填空题 (1)综合布线系统就是用数据和通信电缆、光缆、各种软电缆及有关连接硬件构成的通用布线系统,它能支持语音、数据、影像和其他控制信息技术的标准应用系统。 (2)综合布线系统是集成网络系统的基础,它能满足数据,语音及视频图像等的传输要求,是智能大厦的实现基础。 (3)在GB 50311-2007《综合布线系统工程设计规范》国家标准中规定,在智能建筑工程设计中宜将综合布线系统分为基本型、增强型、综合型三种常用形式。 (4)综合布线系统包括7个子系统,分别是工作区子系统,水平子系统,垂直子系统,管理间子系统,设备间子系统和建筑群子系统,进线间子系统。 (5)在工作区子系统中,从RJ45插座到计算机等终端设备间的跳线一般采用双绞线电缆,长度不宜超过5米。 (6)安装在墙上或柱上的信息插座应距离地面30厘米以上。 (7)水平子系统主要由信息插座,配线架,跳线等组成。 (8)水平子系统通常由 4 对非屏蔽双绞线组成,如果有磁场干扰时可用屏蔽双绞线。 (9)垂直子系统负责连接管理间子系统到设备间子系统,实现主配线架与中间配线架的连接。 (10)管理间子系统是连接垂直子系统和水平干线子系统的设备,其配线对数由管理的信息点数来决定。2.选择题(部分为多选题) (1)GB50311-2007《综合布线系统工程设计规范》中,将综合布线系统分为几个子系统。( C ) A 5 B 6 C 7 D 8 (2)工作区子系统又称为服务区子系统,它是由跳线与信息插座所连接的设备组成。其 中信息插座包括以下哪些类型( ABC ) A墙面型 B地面型 C桌面型 D吸顶型 (3)常用的网络终端设备包括哪些( ABD ) A计算机 B电话机和传真机 C汽车 D 报警探头和摄像机 (4)设备间入口门采用外开双扇门,门宽一般不应小于多少米(B ) A 2米 B 1.5米 C 1米 D 0.9米 (5)在网络综合布线工程中,大量使用网络配线架,常用标准配线架有哪些( BD ) A 18口配线架 B 24口配线架 C 40口配线架 D 48口配线架 (6)为了减少电磁干扰,信息插座与电源插座的距离应大于多少毫米(C ) A 100毫米 B 150毫米 C 200毫米 D 500毫米 (7)按照GB 50311国家标准规定,铜缆双绞线电缆的信道长度不超过多少米( C ) A 50米 B 90米 C 100米 D 150米 (8)按照GB 50311国家标准规定,水平双绞线电缆最长不宜超过多少米(B ) A 50米 B 90米 C 100米 D 150米 (9)总工程师办公室有下列哪些信息化需求(ABC ) A 语音 B数据 C 视频 D 用餐。 (10)在水平子系统的设计中,一般要遵循以下哪些原则(ABC ) A 性价比最高原则 B 预埋管原则 C水平缆线最短原则 D 使用光缆原则 3. 思考题 (1)在工作区子系统的设计中,一般要遵循哪些原则 (2)水平子系统中双绞线电缆的长度为什么要限制在90米以内 (3)管理间子系统的布线设计原则有哪些 (4)GB 50311-2007《综合布线系统工程设计规范》国家标准第7.0.9条为强制性条文, 必须严格执行。请问该条是如何规定的为什么这样规定 (5)请绘制出设备间子系统的原理图。

综合布线总结与心得

综合布线总结与心得 综合布线是一种模块化的、灵活性极高的建筑物内或建筑群之间的信息传输通道。它既能使语音、数据、图像设备和交换设备与其它信息管理系统彼此相连,也能使这些设备与外部相连接。它还包括建筑物外部网络或电信线路的连接点与应用系统设备之间的所有线缆及相关的连接部件。综合布线系统由不同系列和规格的部件组成,其中包括:传输介质、相关连接硬件(如配线架、连接器、插座、插头、适配器)以及电气保护设备等。这些部件可用来构建各种子系统,它们都有各自的具体用途。 综合布线系统大致可以分为七个部分,分别是:工作区;配线子系统;干线子系统;建筑群子系统;设备间;进线间与管理。 实际上布线工作中要遵循一定的规律,此规律不仅体现于结构化布线工程实施所要遵循的相关规范和标准,还需要符合在工程中摸索出来的许多经验和教训。综合布线作为已经成熟的行业,在经历了大量实践的基础上积累了许多可以借鉴的实用经验。布线过程管理混乱、工艺落后、技术陈旧,都会给施工单位本身带来工程质量、成本和进度上的不足。使用先进规范的施工操作规程是企业取得效益和立足市场的必由之路。 一、工程应用综合布线工程一般步骤为:调研—方案设计—土建施工—技术安装—信息点测试—文档整理—维护。 (1)调研:主要任务是询问客户网络需求,现场勘察建筑,根据建筑平面图等资料去结算线材的用量,信息插座的数目和机柜定位、数量,做出综合布线调研报告; (2)布线方案设计:根据前期勘察数据做出布线材料预算表、工程进度安排表; (3)土建施工:协调施工队与业主进行职责商谈,提出布线许可,主要是钻孔、走线、信息插座定位、机柜定位、做线标识; (4)技术安装:主要是打信息模块,打配线架、机柜内部安装; (5)信息点测试:一般测试,采用12点测试仪,单人可以进行,效率较高,主要测试通断情况,可打印出详细的测试报告; (6)文档管理:最终要提供交给客户的峻工报告(材料实际用量表、测试报告、楼层(楼群)配线表,为日后维护提供数据依据; (7)维护:当线路出现故障时,快速进行响应。 二、技术 1、PVC管槽施工过程时,一定要把线先划好,如果不预先画划好线直接施工很容易造成PVC 走线不水平或垂直,虽然这样前期工作花时间较多,但方便以后PVC装钉。 2、打室外通到室内墙孔时,要注意先量好准确的位置,然后才分别从两边钻孔,先用小钻定位,再用中钻打通,再改大钻加大孔径,这样可避免打裂墙面。 3、拉线。这一环节十分重要,如果决策或测量有误,将造成不可挽回的损失。 4、打信息模块时,有一点非常要注意:由于特殊原因,打模块时外皮离模块大约要有1CM,因为这类模块较长,不照上面做的话,装好的模块那防尘板会难移动,失去弹性,所以都要这样做才能确保模块安装的合理。

苹果电脑MACbook-Air快捷键大全

苹果电脑MACbook-Air快捷键大全

苹果电脑MACbook Air快捷键大全要使用快捷键或组合键,您可以同时按修饰键和字符键。例如,同时按下Command 键(标有符号的按键)和“c”键会将当前选中的任何内容(文本、图形等等)拷贝至夹纸板。这也称作Command-C 组合键(或快捷键)。 许多组合键中都包含修饰键。修饰键将改变Mac OS X 对其他按键或鼠标点按动作的解释 方式。修饰键包括Command、Control、Option、Shift、Caps Lock 和fn 键(如果您的键盘有fn 键)。 以下是出现在Mac OS X 菜单中的修饰键符号: (Command 键)也叫苹果键,基本相当于pc的Ctrl键 (Control 键) (Option 键)-“Alt”可能也出现在此键上(Shift 键) (Caps Lock 键)- 切换Caps Lock 开或关 fn(功能键) Finder 快捷键

Command-C 拷贝所选项/文本至夹纸板 Shift-Command-C 打开“电脑”窗口 Command-D 复制所选项 Shift-Command-D 打开桌面文件夹 Command-E 推出 Command-F 查找任何匹配Spotlight 属性的内容Shift-Command-F 查找Spotlight 文件名匹配项 Option-Command-F 导航到已打开的Spotlight 窗口中的搜索栏 Shift-Command-G 前往文件夹 Shift-Command-H 打开当前所登录用户帐户的个人文件夹Command-I 显示简介 Option-Command-I 显示检查器 Control-Command-I 获得摘要信息 Shift-Command-I 打开iDisk Command-J 调出“显示”选项 Command-K 连接服务器 Shift-Command-K 打开“网络”窗口 Command-L 为所选项制作替身 Command-M 最小化窗口 Option-Command-M 最小化所有窗口 Command-N 新建Finder 窗口 Shift-Command-N 新建文件夹 Option-Command-N 新建智能文件夹 Command-O 打开所选项 Shift-Command-Q 注销 Option-Shift-Command-Q 立即注销 Command-R 显示(替身的)原身 Command-T 添加到工具条 Shift-Command-T 添加到个人收藏

sai的快捷键

M矩形、椭圆选框工具 C裁剪工具 V移动工具 L套索、多边形套索、磁性套索 W魔棒工具 J喷枪工具 B画笔工具 S像皮图章、图案图章 Y历史记录画笔工具 E像皮擦工具 N铅笔、直线工具 R模糊、锐化、涂抹工具 O减淡、加深、海棉工具 P钢笔、自由钢笔、磁性钢笔 +添加锚点工具 -删除锚点工具 A直接选取工具 T文字、文字蒙板、直排文字、直排文字蒙板 U度量工具 G直线渐变、径向渐变、对称渐变、角度渐变、菱形渐变 K油漆桶工具 I吸管、颜色取样器 H抓手工具 Z缩放工具 D默认前景色和背景色 X切换前景色和背景色 Q切换标准模式和快速蒙板模式 F标准屏幕模式、带有菜单栏的全屏模式、全屏模式 Ctrl临时使用移动工具 Alt临时使用吸色工具 空格临时使用抓手工具 Enter打开工具选项面板 0至9快速输入工具选项(当前工具选项面板中至少有一个可调节数字) [或]循环选择画笔 Shift+[选择第一个画笔 Shift+]选择最后一个画笔 Ctrl+N建立新渐变(在”渐变编辑器”中) Ctrl+N新建图形文件 Ctrl+Alt+N用默认设置创建新文件 Ctrl+O打开已有的图像 Ctrl+Alt+O打开为... Ctrl+W关闭当前图像

Ctrl+S保存当前图像 Ctrl+Shift+S另存为... Ctrl+Alt+S存储副本 Ctrl+Shift+P页面设置 Ctrl+P打印 Ctrl+K打开“预置”对话框 Alt+Ctrl+K显示最后一次显示的“预置”对话框 Ctrl+1设置“常规”选项(在预置对话框中) Ctrl+2设置“存储文件”(在预置对话框中) Ctrl+3设置“显示和光标”(在预置对话框中) Ctrl+4设置“透明区域与色域”(在预置对话框中) Ctrl+5设置“单位与标尺”(在预置对话框中) Ctrl+6设置“参考线与网格”(在预置对话框中) Ctrl+3外发光效果(在”效果”对话框中) Ctrl+4内发光效果(在”效果”对话框中) Ctrl+5斜面和浮雕效果(在”效果”对话框中) A应用当前所选效果并使参数可调(在”效果”对话框中) Alt+-或+循环选择混合模式 Ctrl+Alt+N正常 Ctrl+Alt+L阈值(位图模式) Ctrl+Alt+I溶解 Ctrl+Alt+Q背后 Ctrl+Alt+R清除 Ctrl+Alt+M正片叠底 Ctrl+Alt+S屏幕 Ctrl+Alt+O叠加 Ctrl+Alt+F柔光 Ctrl+Alt+H强光 Ctrl+Alt+D颜色减淡 Ctrl+Alt+B颜色加深 Ctrl+Alt+K变暗 Ctrl+Alt+G变亮 Ctrl+Alt+E差值 Ctrl+Alt+X排除 Ctrl+Alt+U色相 Ctrl+Alt+T饱和度 Ctrl+Alt+C颜色 Ctrl+Alt+Y光度 海棉工具+Ctrl+Alt+J去色 海棉工具+Ctrl+Alt+A加色 减淡/加深工具+Ctrl+Alt+W暗调 减淡/加深工具+Ctrl+Alt+V中间调

网络综合布线 实 训 总 结 报 告

岗前实训报告2012/2013学年第1学期 网络综合布线 实训总结报告 姓名:张兴睿 班级:网络1001 指导教师:袁德利于桂宾实训时间:2012.9.23~2012.10.12 承德石油高等专科学校 计算机与信息工程系

目录 前言 1.实训的主要内容和知识点 1.1网络综合布线知识介绍 结构化布线系统由工作区子系统、配线(水平)子系统、干线(垂直)子系统、设备间子系统、管理子系统、建筑群子系统六个子系统组成。 1.建筑群子系统(CAMPUS SUBSYSTEM)。 2.设备子系统(EQUIPMENT SUBSYSTEM) 3.垂直干线子系统(RISER BACKBONE SUBSYSTEM)。 4.管理子系统(ADMINISTRATION SUBSYSTEM)。 5.水平布线子系统(HORIZONTAL SUBSYSTEM)。 6.工作区子系统(WORK AREA SUBSYSTEM)。 各子系统所实现的功能如下: 1.工作区子系统由配线(水平)布线系统的信息插座延伸到工作站终端设备处的连接电缆及 适配器组成,每个工作区根据用户要求,设置一个电话机接口和1至2个计算机终端接口。 2.配线(水平)子系统由工作区用的信息插座,每层配线设备至信息插座的配线电缆、楼层 配线设备和跳线等组成。 3.干线(垂直)子系统由设备间的配线设备和跳线,以及设备间至各楼层配线间的连接电缆 组成。 4.设备间子系统由综合布线系统的建筑物进线设备,电话、数据、计算机等各种主机设备及 其保安配线设备等组成。 5.管理子系统设置在每层配线设备的房间内,是由交接间的配线设备,输入/输出设备等组 成。 6.建筑群子系统由二个及以上建筑物的电话、数据、电视系统组成一个建筑群子系统,它 是室外设备与室内网络设备的接口,它终结进入建筑物的铜缆和/或光缆,提供避雷及电源超荷保护等。 1.2综合布线工具 剥线钳:用来剥网线保护套管 打线钳:把双绞线打到配线架上 压线钳:把水晶头与正确的线序进行压合 网络测线仪:测试网线的联通性 配线架:将多组双绞线进行组合 理线架:理线 1.3相关国家标准文件的介绍: GB50311-2007综合布线系统工程设计规范; GB50312-2007综合布线系统工程验收规范;

网络综合布线的总结

1、建筑群布线有几种方法?比较它们的优缺点? 答:建筑群布线有架空,直埋,和地下管道三种方法优缺点比较: 架空:架空布线法通常只用于有现成电缆杆,而且线缆的走线方式不是主要考虑因素的场合。虽然成本不高,但是影响美观,而且保密性、安全性也差。 直埋:直埋布线方法可以保持建筑物在原貌,直埋布线法优于架空布线法 地下管道:由于管道是用耐腐蚀性的材料做成的,所以这种方法给谨慎提供了最好的机械保护,使受损而维修的机会减少到最低程度,并且能保持建筑物的原貌。 2、工程监理的依据有哪些?其实施步骤有哪些? 答:依据:1,国家及行业标准;2,国家、地方法规及相关文件 步骤: 1) 施工准备阶段监理 2) 施工阶段的监理,施工前的环境检查;对施工前承包单位的器材检查给予确认;设备安装的随工检查;电缆和光缆的布放随工检查及隐蔽工程签证;电缆和光缆终端的随工检查;工程总验收 3) 保修阶段的监理 3、简述配线子系统的设计要点。 4、简述综合布线工程施工应该遵循的基本要求。 1,新建或扩建的建筑物的综合布线工程的安装施工,某些综合布线工程除了数据通信外,还有语音、有线电视、监控系统等,因此,施工前必须按照相关国家标准和行业标准的要求组织施工 2,综合布线中所得到的缆线、布线部件应符合国家通信行业标准 3,必须制定一套规范的组织机构、保障施工的顺利进行 4,必须加强施工质量管理 5,施工过程中,要按照同意的管理标识,对线缆、配线架、信息插座等进行标记 5、简述在布线施工前应该进行哪些准备工作? 施工后应该进行哪些收尾工作? 6、答:施工前的准备: 1,熟悉工程设计和施工图纸 2,编制施工方案 3,施工场地的准备 4,高工工具的准备 5,环境检查 6,器材检查 施工后的收尾工作: 1验收内容;2竣工技术文档;3竣工验收 6、综合布线工程的竣工文档包含哪些文件? 五、综合布线系统的基本含义是什么?与传统布线相比,具有哪些特点?为什么要实现综合布线?综合布系统划分成几个子系统?各子系统由哪些具体组成?(10分) 答:综合布线系统是由许多部件组成的,主要有传输介质、线路管理硬件、连接器、插座、插头、适配器、传输电子线路、电气保护设施等,并由这些部件来构造各种子系统。理想的布线系统表现为:支持语音应用、数据传输、影像影视、而且最终能支持综合型的应用 特点:结构清晰便于管理;材料同意、先进、适应今后的发展;灵活性强,适应各种工作的要求;节约费用,提高系统的可靠性。 原因:提高综合布线工程的性价比,方便管理,方便扩展,系统具有很高的灵活性。 综合布线系统分为6个子系统:工作区子系统,管理间子系统,水平干线子系统,垂直干线子系统,楼宇间子系统,设备间子系统 1、请简单介绍综合布线系统的组成和各子系统的功能。 1. 建筑群子系统 2. 设备子系统 3. 垂直干线子系统 4. 管理子系统 5. 水平布线子系统 6. 工作区子系统各子系统所实现的功能如下: