Modelsim与NCVerilog仿真理解

Modelsim/NCVerilog 仿真理解

一、modelsim仿真

这里以交通信号灯为例介绍modelsim的仿真方法。

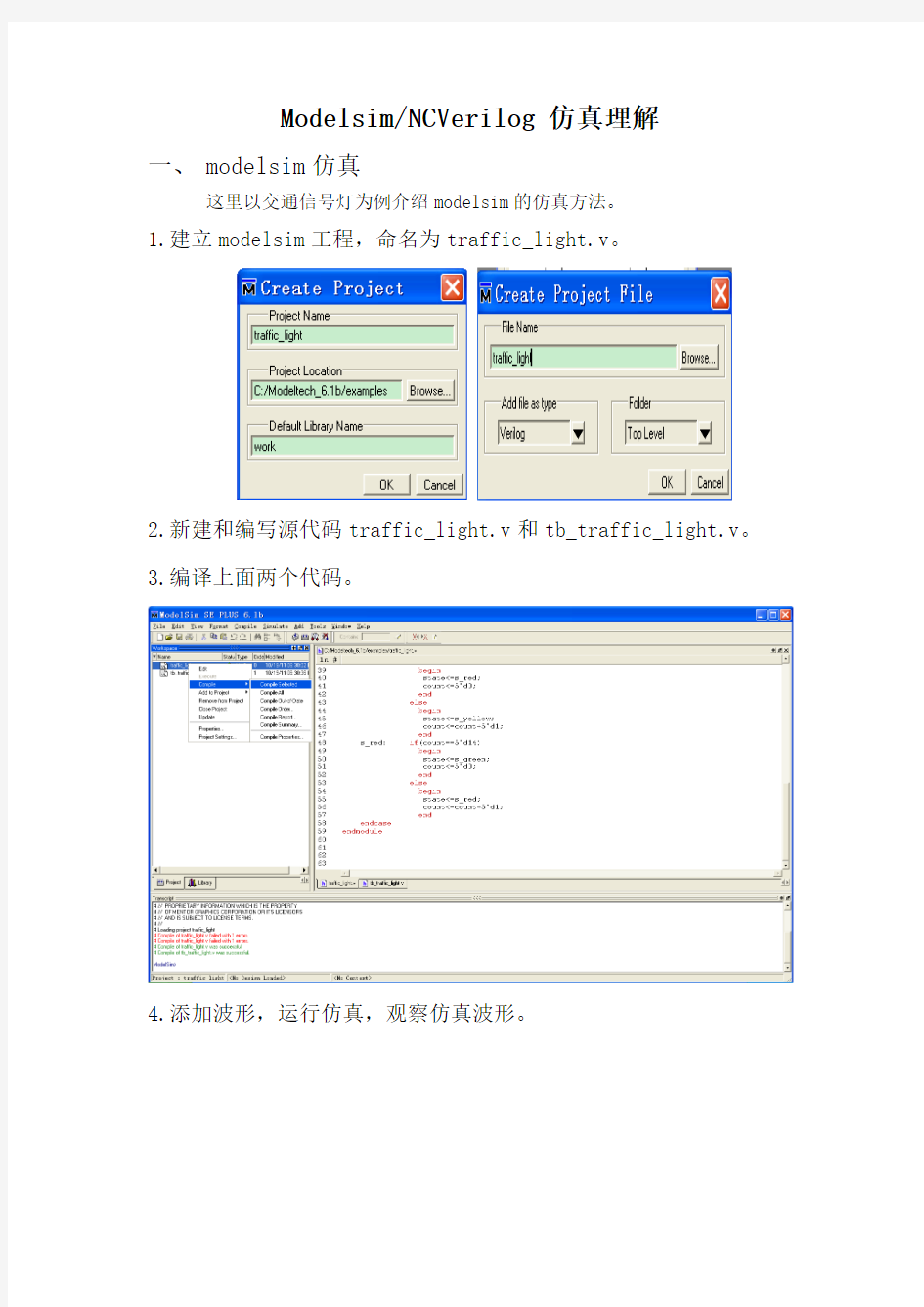

1.建立modelsim工程,命名为traffic_light.v。

2.新建和编写源代码traffic_light.v和tb_traffic_light.v。

3.编译上面两个代码。

4.添加波形,运行仿真,观察仿真波形。

二、NCVerilog仿真

1.编写代码traffic_light.v和tb_traffic_light.v.

2.编写批处理文件runallcode.bat,里面的内容为

TITEL %cd%

ncverilog -f runfilelist.f +debug +notimingcheck

+access+rwc

pause

3.编写文件列表文件runfilelist.f,里面包含了要仿真的代码traffic_light.v和tb_traffic_light.v.

4.运行runallcode.bat,生成fscb格式的波形文件,通过

debussy观察波形。

三.Modelsim 和NCVerilog对比

NCVerilog特点

●多种语言:verilog/vhdl;

●多种等级:behavioral, rtl, gate;

● event-driven, cycle-based;

●混合信号:模拟,数字

Modelsim特点

?由Model技术公司开发

?工业上最通用的仿真器之一

?可在Verilog 和 VHDL仿真

对比:

在rtl级或行为级,这两种仿真器都有不错的表现,速度差别

不是很大但是在门级仿真,nc速度最快,modelsim要慢很多。

附录代码

`timescale 1ns/1ps

module traffic_light(clk,rst,state);

input clk,rst;

output[1:0] state;

reg[1:0] state;

reg[4:0] count;

parameter s0=2'b0,

s_green=2'b01,

s_yellow=2'b10,

s_red=2'b11;

always@(posedge clk or posedge rst) if(rst)

begin

state<=s0;

count<=5'd0;

end

else

case(state)

s0:

begin

state<=s_green;

count<=5'b0;

end

s_green: if(count==5'd24)

begin

state<=s_yellow;

count<=5'd0;

end

else

begin

state<=s_green;

count<=count+5'd1;

end

s_yellow: if(count==5'd1)

begin

state<=s_red;

count<=5'd0;

end

else

begin

state<=s_yellow;

count<=count+5'd1;

end

s_red: if(count==5'd14)

begin

state<=s_green;

count<=5'd0;

end

else

begin

state<=s_red;

ount<=count+5'd1;

end

endcase

endmodule

测试代码:

`timescale 1ns/1ps

module tb_traffic_light();

reg clk,rst;

wire[1:0] state;

initial

begin

clk=0;

rst=0;

#20 rst=1;

#50 rst=0;

end

always #5 clk=~clk;

traffic_light traffic_light_cmpt(.clk(clk),

.rst(rst),

.state(st ate));

initial

begin

$fsdbDumpfile("traffic_light.fsdb");

$fsdbDumpvars(0,tb_traffic_light);

#2000000 $finish;

end

endmodule

modelsim使用 + 前仿真 + 后仿真 + verilog

Modelsim 6.0 使用教程 1. Modelsim简介 Modelsim仿真工具是Model公司开发的。它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。 对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。 2.安装 同许多其他软件一样,Modelsim SE同样需要合法的License,通常我们用Kengen产生license.dat。 ⑴.解压安装工具包开始安装,安装时选择Full product安装。当出现Install Hardware Security Key Driver时选择否。当出现Add Modelsim To Path选 择是。出现Modelsim License Wizard时选择Close。 ⑵.在C盘根目录新建一个文件夹flexlm,用Keygen产生一个License.dat,然后 复制到该文件夹下。 ⑶.修改系统的环境变量。右键点击桌面我的电脑图标,属性->高级->环境变量-> (系统变量)新建。按下图所示内容填写,变量值内如果已经有别的路径了, 请用“;”将其与要填的路径分开。LM_LICENSE_FILE = c:\flexlm\license.dat

Quartus ii 10.0教程(包含modelsim仿真)

Quartus ii 10.0教程 说明 本文的部分章节,来源于本人翻译的Terasic DE2-115的英文入门文档。 平台 硬件:艾米电子EP2C8-2010增强版套件 软件:Quartus II 10.0 + ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容 ?典型的CAD流程 ?开始 ?新建工程 ?录入Verilog设计 ?编译设计 ?引脚分配 ?仿真设计电路 ?编程及配置到FPGA器件 ?测试设计电路 典型的CAD流程 计算机辅助设计(CAD)软件,使得运用可编程逻辑器件实现所需逻辑电路,变得容易。比如现场可编程门阵列(FPGA)。典型的FPGA CAD设计流程如图1所示。

图1 典型的FPGA CAD设计流程 CAD流程包含以下步骤: ?设计输入——所需电路可通过原理图方式或硬件描述语言方式(如Verilog或VHDL)进行设计。 ?综合——输入的设计被综合进入由逻辑元素(LEs,FPGA芯片提供)组成的电路中。 ?功能仿真——综合电路被测试以验证其功能是否正确,次仿真不考虑时序因素。 ?布局布线——CAD Fitter工具决定网表中定义的LEs如何布置成FPGA芯片中的实际LEs。 ?时序分析——分析已布局布线电路中的不同路径的传播延迟,用以指示所需电路的性能。 ?时序仿真——测试已布局布线电路,验证其是否在功能和时序上都正确。 ?编程及配置——设计的电路,通过编程配置开关,被实现到一个物理的FPGA芯片。 配置开关用于配置LEs和建立所需线路连接。 本指南介绍Quartus II软件的基本特征。展示如何使用Verilog硬件描述语言来设计和实现电路。使用GUI来实现Quartus II指令。通过本份指南,读者将学习到: ?新建工程 ?使用Verilog代码录入设计 ?将综合的电路布局到Altera FPGA ?分配电路的输入输出到FPGA上的指定引脚 ?仿真设计电路 ?编程配置艾米电子EP2C8核心板上的FPGA芯片 1. 开始 在Quartus II中设计的每个逻辑电路或子电路,叫做一个工程。软件每次运行一个工程,并将所有信息保存在单一文件夹中。欲开始一个新的逻辑电路设计,第一步就是新建一个文件夹来保存文件。为了保存本指南的设计文件,在D盘新建introtutorial文件夹。指南者运行的范例为一个简单的双路灯控电路。 打开Quartus II软件,将看到类似于图2的画面。该显示画面包括若干窗口,用户可使用鼠标选择,以访问Quartus II软件的相关功能。Quartus II提供的大多数命令都可用菜单形式来访问。例如,在图2中,在File标签下点击左键,可打开如图3所示的菜单。用左键单击Exit可退出Quartus II软件。

modelsim仿真小结

Modelsim仿真小结 Modelsim的基本仿真流程大致分以下几个步骤:建库、编译工程、前后仿真、调试等。Modelsim仿真既可以在modelsim界面操作,也可以用do文件实现,这里结合学习的教程、网上看到的资料,和实际遇到的一些问题,分别做一整理小结。 1.建库 建库包括Altera库和Xilinx库,同时都包括Verilog和VHDL。这里只建了Verilog库,VHDL和Verilog步骤相同。 对于Altera库主要包括lpm元件库、Mega_Function库atera_mf、altera原语库altera_primitive和各器件系列模型库。前三种是调用altera模块的必备库,第四种是进行综合后功能仿真和布线后时序仿真需要的库,和器件系列有关,只选对应系列即可。 Altera库创建和编译步骤如下: a)在Modelsim安装目录下新建文件夹,命名altera_lib,以存放编译后的库文件,可 以在altera_lib下新建Verilog和VHDL两个子文件夹,分别存放Verilog和VHDL库。 b)打开Modelsim,新建Library,file ->new->library .. c)如下图,创建lpm库,路径E:\modeltech_10.1a\altera_lib\Verilog\lpm

d)添加库文件,并编译,compile -> compile …,出现compile source files窗口, library 指定到lpm下,查找范围,选quartus安装目录下… eda\sim_lib目录里的仿真原型文件:220model.v ,点c ompile ,点done。 到此,lpm库建立完毕。 e)同理,建立altera_mf库添加altera_mf.v ,建立primitive库添加altera_primitive.v 建立各系列的模型库,命名可用系列名加_ver“xxx_ver”,也可随意吧,添加各系列的xxx_atoms.v。 这里,也可以把以上库放在一个文件夹,这样做简单,一次就搞定,分开也就是条理清楚,没人去看,所以没必要。 f)修改modelsim.ini文件,为的是让modelsim能自动map到已经编译的这些库上。 先去掉只读属性,在[Library]和[vcom]之间加上:库名=库路径[绝对路径或者相对路径],相对路径是相对于modelsim安装路径,modelsim安装路径用$MODEL_TECH 表示。 这里所有库都放在E:\modeltech_10.1a\altera_lib下,库名是altera_lib,这里只添加一句:altera_lib = E:\modeltech_10.1a\altera_lib g)保存退出,改回modelsim.ini只读属性,防止乱改。至此altera库建立完毕。 Xlinx库创建和编译步骤如下: 相比altera,xilinx建库很方便。xilinx有批处理命令,直接在console命令窗口,输入compxlib命令,调出编译库的窗口,先改掉modelsim安装目录下modelsim.ini只读属性。设置如下图:

ModelSim的前后仿真(Quartus)

利用Quartus5.0实现功能仿真 1)打开一个工程文件。 2)打开Settings设置栏,选择Fitting Settings下的Simulator栏。在右边出现的设置栏中将 “Simulation Mode”的下拉菜单选择“Functional”,即可以实现软件下的功能仿真。(下拉菜单中有“Functional”、“Timing”和“Timing using Fast Timing Model”,分别代表可以在Quartus软件下实现功能仿真,时序仿真和快速时序仿真。最后一项一般不选,如果在Settings->Timing Requirement->More Settings下“Report Combined Fast/Slow Timing” 选项设为“On”,就可以选择最后一项。编译的报告里也会分别列出最快和最慢的时序报告。) 3)选择“Processing”菜单下的“Generate Functional Simulation Netlist”命令,否则将无法 启动仿真。 4)新建一个波形仿真文件,文件后缀名为.vwf。选择File菜单下的New->Other Files->Vector Waveform File。如下图所示,左边空白栏处是节点名的列表区,右边空白栏处是仿真波形的显示区。波形编辑窗口默认时间为1us,如果想改变仿真时间,可以选择Edit菜单下End Time,在弹出的对话框中选择需要的时间。将新建的波形仿真文件保存下来。

5)将需要仿真的信号加入波形编辑窗口。在列表区任一位置双击或者点击右键选择“Insert Node or Bus…”,弹出的对话框点击“Node Finder”按钮。在“Node Finder”界面中点击“List”按钮,有关信号的列表会出现在界面的左边,双击需要观察的信号加入至界面右边。如果工程中用到了很多信号,在左边列表中也会显示很多(Named编辑框默认的是*通配符),可以在Named编辑框中添加需要的信号名称实现模糊查找。界面中“Filter”下拉框中默认的是“Pins: all”,也就是说将要列出的信号都是IO管脚。如果需要观察一些内部信号,可以改变下拉框的参数,比如“Registers: Pre-Synthesis”。下图显示了仿真信号加入波形编辑窗口的情况。对于有些总线信号可以改变其显示的进制格式,比如二进制、八进制、十进制和十六进制。在列表中对应信号点击右键选择 “Properties”,弹出的对话框中选择“Radix”下拉框实现进制的转换。

ModelSim作布局布线后仿真的库问题

ModelSim作布局布线后仿真的库问题 Modelsim是目前最流行的应用最广泛的FPGA仿真器,是Mentor Graphics的子公司Model T echnology开发的。因为Modelsim好学易用,调试方便,仿真速度快,功能强大,所以很多芯片厂商的开发系统都OEM Mentor Graphics公司的Modelsim仿真器,包括Xilinx,Alter a,Lattice和Actel等。Modelsim是一个单内核仿真器,同一个内核可以进行VHDL仿真、V erilog仿真和VHDL/Verilog混合仿真;支持所有的VHDL和Verilog标准;采用直接编译技术 (Direct-Compiled),大大提高了HDL编译和仿真速度。 Modelsim支持三个层次的仿真:RTL仿真、综合后仿真和布局布线后仿真。为了加快仿真速 度,一般情况下设计中调用的库都是已经进行编译过的,然后对设计进行仿真,此时仿真器直接调用库中已经编译过的单元,而不是再次对设计中的单元模块进行编译。所以如果要对设计进行综合后仿真和布局布线后仿真,必须先对设计中调用的库进行编译处理。这也是本文的重点内容。因为每个厂商的库不一样,而且同一个厂商,不同的器件库就有可能不同,所以下面就目前国内比较常用的几个公司的芯片的库问题分别进行探讨。1.Xilinx公司的器件: 其库的处理方式有两种,一种是在Xilinx的网站上,我们可以下载到压缩文件xilinx_lib _4.zip,解压缩后有一个xilinx_lib_4.tcl(将来的版本可能会升级)。单独运行Models im,然后在工具菜单中有一项是执行宏(这里Modelsim5.5 和5.6、5.7有一些差异,不过在5.5中仍可以找到执行宏Execute Macro),运行xilinx_lib_4.tcl后可以看到。 你可以根据你的厂商软件版本选择,指定Xilinx 的安装路径,在Install Path中指定你编 译后的数据将要放的目录位置(可以是任何一个目录,最好是设计者数据盘中的某个目录,因为库编译一次就可以了,重新安装软件不需要重新编译库)。对于Xilinx作布局布线后仿真只需要simprim库即可;如果要作综合后仿真,就需要编译Unisim库;如果设计中调用了 CoreGen产生的核就需要编译CoreGen库。这应该根据设计者的具体情况进行选择。 如果编译完了后,在Modelsim中库会自动变为标准库(注意:Xilinx提供的早期脚本文件作不到这一点)。所谓标准库,也就是说这个库会和IEEE这些库一样,当Modelsim启动时,这 些库会自动加载,里面的单元在VHDL代码中可以随意调用。比如:在布局布线后的VHDL 文 件中大家可以看到Library simprim这样的语句。当然也可以自己手动改变这些库的性质,只用修改在Modelsim安装路径下的Modelsim.ini文件即可。比如:修改后的Modelsim.ini 可以看到为 [Library] std = $MODEL_TECH/../std ieee = $MODEL_TECH/../ieee verilog = $MODEL_TECH/../verilog std_developerskit = $MODEL_TECH/../std_developerskit synopsys = $MODEL_TECH/../synopsys modelsim_lib = $MODEL_TECH/../modelsim_lib

modelsim完美教程

准备事项 1.ModelSim试用版下载 2.范例程序下载(史丹佛大学一门课的期末专题Implememtation of Viterbi Decoder:constrain length K=3, code rate R=1/2, register-exchange) 整个project共含7个Verilog程序:system.v (top-level) |-- clkgen.v |-- chip_core.v |-- controller.v |-- spu.v |-- acs4.v |-- acs1.v (或是另外一个Verilog的简单例子,可以从C:\ SynaptiCAD\ Examples\ TutorialFiles\ VeriLoggerBasicVerilo gSimulation\ add4.v and add4test.v) (或是另外一个VHDL的简单例子,可以从C:\ Modeltech_5.7e\ examples\ adder.vhd and testadder.vhd) ModelSim PE /LE /SE 差别在哪? 本篇文章内容主要在教导软件使用,以Verilog程序为范例。假设各位读者已经熟悉Verilog,废话不多说,让我们马上来见识一下ModelSim ... 快速上手四部曲:建立Project、引进HDL Files、Compile、模拟(Simulate/Loading and Run) 1.建立一个新的Project 1-1 第一次执行程序时,可以从[开始] \ [程序集] \ ModelSim SE \ ModelSim;或是执行ModelSim在桌面的快捷方式

Modelsim常见问题

Modelsim 常见问题 Q1:设计中用到厂商提供的IP时,编译时出现“(vopt-3473) Component instance "XXXX" is not bound.” A1:编译时,需要把所需的Libray添加到编译命令中,如“vsim -L C:/Modeltech_6.2b/xilinx_lib/XilinxCoreLib ......”。 Q2:vhdl和verilog混合仿真时,vhdl和verilog代码中会调用同一个组件,但是他们分别来自不同的library,如unisim和unisim_ver,它们相互并不通用,及verilog不能调用unisim_ver的组件,会造成组件找到却没办法绑定的错误,如:“Port 'Q' not found in the connected module”? A2:当仿真时,由于vhdl代码中会指定从那个库文件里面提取,而verilog代码中没有,所以使用vsim命令时,把verilog所需的库放在第一个,而后放vhdl 所需的库,这样,verilog会从unisim_ver代码开始查询组件。 Q3:"ERROR: ../

ModelSim入门指导答辩

QUESTA-SIM(QuestaSim)10.2入门指南平台 软件:Questa-Sim 10.2 版本Starter Edition,也适用于高版本的ModelSim软件。内容 一. 设计流程 典型设计流程包括如下所示: (1)设计输入 设计的行为或结构描述 (2)RTL仿真(ModelSim) 功能仿真 验证逻辑模型(没有使用时间延迟) 可能要求编辑设计 (3)综合 把设计翻译成原始的目标工艺 最优化——合适的面积要求和性能要求 (4)布局和布线 映射设计到目标工艺里指定位置 指定的布线资源应被使用 (5)门级仿真(ModelSim) 时序仿真 验证设计一旦编程或配置将能在目标工艺里工作 可能要求编辑设计 (6)时序分析 (7)验证合乎性能规范 可能要求编辑设计 (8)版图设计 (9)仿真版图设计 (10)在板编程和测试器件 使用QuestaSi/ModelSim仿真的基本流程为: 图1.1 使用QuestaSim仿真的基本流程 2 开始 1.1 新建工程 打开QuestaSim后,其画面如图2.1所示。

图2.1 QuestaSim画面 1. 创建工作目录E:/QuestaSim/, 在其路径下创建子文件夹/ip、/prj、/rtl、/tb, prj是QuestaSim工程主文件夹,ip是仿真模型目录,rtl 是代码目录,tb是testbench目录。 2. 选择File>New>Preject创建一个新工程。打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。一般情况下,设定Default Library Name为work。指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。该对话框如图2.2所示,此外还 允许通过修改初始化文件QuestaSim.ini文件来映射库设置。 图2.2 创建工程的对话框 2. 设置Project Name为BG0806,Project Location为E:/QuestaSim/prj, 勾选Copy Library Mappings ,点击OK。 3. 出现Add Items to the Project的对话框,如图2.3所示,

modelsim仿真详细过程

由于我们只需要了解仿真的完整过程,所以不需要自己写源文件和测试文件(也称为testbench)。一下就是简单的源文件和测试文件(亲自测试过)。 //源文件 module compare(equal,a,b); input a,b; output equal; assign equal=(a==b)?1:0; endmodule //测试文件 `timescale 1ns/1ns `include"./compare.v" module comparetest; reg a,b; wire equal; initial begin a=0; b=0; #100 a=0;b=1; #100 a=1;b=1;

#100 a=1;b=0; #100 $stop; end compare compare1(.equal(equal),.a(a),.b(b)); endmodule 有了源文件和测试文件下面就开始用modelsim进行仿真了。 步骤一:新建工程和.v文件(也就是源文件和测试文件) 打开modelsim软件,点击file,选择new—>project 然后就会弹出下面窗口: 然后在project name那一栏写上工程名(随便去,一般是字母),在project location选择工程路径(路径最好没有中文,听说的),然后点OK。进入下个界面:

然后点击小框里面的“create new file”.弹出界面: 在file name中写下源文件名,由于这是比较两数的大小,我取为:compare。在“add file as type”中选择verilog,点OK,然后有:

ModelSim-Altera_6.5仿真入门教程

平台 软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容 1 设计流程 使用ModelSim仿真的基本流程为: 图1.1 使用ModelSim仿真的基本流程 2 开始 2.1 新建工程 打开ModelSim后,其画面如图2.1所示。

图2.1 ModelSim画面 1. 选择File>New>Preject创建一个新工程。打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。一般情况下,设定Default Library Name为work。指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。该对话框如图 2.2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。

图2.2 创建工程的对话框 2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D:/led_flow。 图2.3 输入工程信息 当单击OK按钮后,在主体窗口的下方将出现Project标签,如图2.4所示。 图2.4 Project标签

3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。 图2.5 在工程中,添加新项目 2.2 在工程中,添加新项目 在Add Items to the Project对话框中,包括以下选项: ?Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL或文本文件?Add Existing File——添加一个已存在的文件 ?Create Simulation——创建指定源文件和仿真选项的仿真配置 ?Create New Folder——创建一个新的组织文件夹 1. 单击Create New File。打开图 2.6所示窗口。 图2.6 创建工程文件夹 2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。

modelsim问题综述

MODELSIM问题综述 ——阿泽成长路 鉴于最近一直困于modelsim se 10.0c(win32/win64)的安装及破解,在借鉴了度娘提供的好多零散的信息后,今天好好归纳总结下权当做个备忘,也顺便给电子信息、通信专业及做数字系统设计的同学分享我的经验。 安装过程很常规,一直狂击next就ok,只是在安装过程中会产生一个选项(是否使用硬件级别证书),选择yes,即要求重新启动(注意安装路径不允许有中文与下划线)完成安装,度娘也说可以点no,总之对于软件的破解不会产生影响,至于后期的使用还未见太多端倪。在我鼓捣的好多次中有过重启,也有点no,应该不会影响,但我建议还是照软件原意选择安装,值得一提的是安装过程还比较漫长需耐心等待。 在安装后就是软件的破解了。 1.解压modelsim-gcc-4. 2.1-mingw32vc9.zip/modelsim_se_10.0c.rar,然后将解压后的文件()覆盖(粘贴)到安装目录下的win64/win32目录下,如果win64/win32目录下已存在就选择替换,没有就直接保存。 2.打开patch_dll.bat同是在弹出的选项中选择运行MentorKG.exe,此时请耐心等待,正常情况下会弹出LICENSE.TXT文件,将其保存到modelsim10.0c安装目录下(与win64/win32同级存在!!!);然而也可能遇到运行patch_dll.bat但得不到LICENSE.TXT的情况这时就只有从外部直接复制一个LICENSE到安装目录下,至于这个LICENSE的得到就只有从别人那儿copy了。 3.以上步骤之后需要修改环境变量。右键计算机-->属性-->高级系统设置-->环境变量,之后在系统变量中寻找E:\modeltech64_10.0c\license.txt(安装目录因人而异),选择编辑在原来值后加分号,再将变量值改为modelsim10.0c的安装目录+license.txt ,之后一路ok;但如果系统变量中无E:\modeltech64_10.0c\license.txt 则需要新建变量名:LM_LICENSE_FILE,变量值同上,之后ok。 4.运行modelsim破解安装完毕。 另外:在做模拟过程中也许会出现object栏无信号&wave无波形的情况,解决方案如下:现象:仿真时没有“object”,没有波形。 原因:软件本身的优化问题 解决方法:在安装目录下如C:\Modeltech_6.2b目录下找到modelsim.ini文件,将其属性改为可写即将原来选中的“可读”去掉(这一步可能没有,视情况而定)。打开该文件将里面的VoptFlow = 1改为VoptFlow = 0。值得一提的是,如果在修改modelsim.ini之前建立的project,在修改之后仍然会出现没有波形的情况,这时你只需要建立一个新的project 把你的代码移过去就行了。因为在修改modelsim.ini之前建立的project还是默认VoptFlow = 1。 尽情享用吧!!!

ModelSim软件仿真步骤教程

使用ModelSim模擬驗證HDL code 1.在模擬前先準備好我們要模擬的電路檔案(Verilog HDL,TestBench,…) 2. 打開ModelSim,新建一個Project,鍵入Project name 按OK。此處我們的library name 為default library name “work”不必更改。 3.然後再加入我們所要模擬的電路檔案(若尚未準備,可開啟新檔案再將code 鍵入)選Add Existing File,將我們已編輯好的檔案加入。 將我們所需要的檔案加入,按Browse選擇我們所需檔案count.v,

count_test.vt),按下OK。 再將先前所開啟的增加檔案的視窗關閉,按close。 4.按下compile all。

Compile成功沒有顯示出錯誤訊息, 則開始模擬波形 5.按下Simulation, 選擇檔案所在的Library (work), 點選TestBench的Module Name t_Gap_finder 按OK 6.承接上步驟將會跳出以下視窗,若要將所有訊號加入波型中觀察則選擇在 testbench的module name: count_tst按滑鼠右鍵選擇→ Add → Add to Wave。

7.在波型畫面按下Run All開始模擬 跑完後會跳出下面視窗選擇否則可觀察模擬波形,若按下是則會將ModelSim關閉。

8.觀察波形圖是否與功能符合,若與設計不符則修改設計並重複執行Step 4到 Step 8 Testbench語法 `timescale 1 ps/ 1 ps 前面的1ps代表程式中最小的時間單位 後面的1ps代表運算的精準度

Modelsim 仿真步骤总结

Modelsim 仿真步骤总结 Modelsim 仿真主要有以下三个方面:各版本的方法大体一致。(1)建立库并映射库到物理目录; (2)编译源代码(包括testbench); (3)执行仿真; 下面具体演示每一步的操作方法及流程,为力求简洁,其中有多种操方法的只介绍一种。 一)建立库的演示: 步骤为——启动modelsim>点击file菜单>(Change Directory)>new>(project)>library.注括号内的步骤非必须。 1.1)启动modelsim; (1.2)点击file菜单,此时若需更改路径,可以点击其中的Change Directory.(注modelsim会自动默认路径。我们也可以在1.1步骤之前建立一个文件夹用于modelsim的工程,再将路径更改到我们新建的文件夹路径。)

(1.3)点击file子菜单中的new,选择project用于新建立一个modelsim工程。(虽然此步非必须,但是建立一个新工程有益 于接下来整个仿真文件的管理。)

1.4)点击file子菜单new,再点击new下的library,用于建立 一个库。(仔细观察1.3步,新建工程的同时亦可建立库)。 至此,modelsim仿真第一大步建立库的工作完毕。

二)编译源代码(包括testbench): 大家都已知道在quartus中编译源代码的方法,这里说明一下在modelsim中编译源代码及testbench的方法。 步骤为——建立一个新工程(同时建立库)后,会自动提示你四个选项。如图: 选create new file后提示对话框,(也可以在有源文件的情况下选择add existing file到工程中。例如我们用quartus写好文件后,可以用此方法将quartus中的文件添加到modelsim工程中来)让你命名你即将创建的新文件,完毕后,会自动出现一个空白的编辑窗口,在那里输入源代码和testbench。(提示:这样编写完后点保存,便可以直接保存到上面设臵好的work库中。比起另一种方法,不建工程直接建库,再通过菜单栏source添加源

QUARTUSⅡ10波形仿真(ModelSim)入门教程

QUARTUSⅡ10仿真(ModelSim)入门教程平台 软件:ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容 1 设计流程 使用ModelSim仿真的基本流程为: 图1.1 使用ModelSim仿真的基本流程 2 开始 2.1 新建工程 打开ModelSim后,其画面如图2.1所示。 图2.1 ModelSim画面

1. 选择File>New>Preject创建一个新工程。打开的Create Project对话框窗口,可以指定工程的名称、路径和缺省库名称。一般情况下,设定Default Library Name为work。指定的名称用于创建一个位于工程文件夹内的工作库子文件夹。该对话框如图 2. 2所示,此外还允许通过选择.ini文件来映射库设置,或者将其直接拷贝至工程中。 图2.2 创建工程的对话框 2. 按照图2.3所示,设置Project Name为LED_FLOW,Project Location为D:/led_flow。 图2.3 输入工程信息 当单击OK按钮后,在主体窗口的下方将出现Create Project标签,如图2.4所示。 图2.4 Project标签 3. 之后,将出现Add Items to the Project的对话框,如图2.5所示。 图2.5 在工程中,添加新项目 2.2 在工程中,添加新项目 在Add Items to the Project对话框中,包括以下选项:

?Create New File——使用源文件编辑器创建一个新的Verilog、VHDL、TCL或文本文件 ?Add Existing File——添加一个已存在的文件 ?Create Simulation——创建指定源文件和仿真选项的仿真配置 ?Create New Folder——创建一个新的组织文件夹 1. 单击Create New File。打开图 2.6所示窗口。 图2.6 创建工程文件夹 2. 输入文件名称:LED_FLOW,然后选择文件类型为Verilog。 图2.7 输入工程文件信息 3. 单击OK,关闭本对话框。新的工程文件将会在工程窗口显示。单击Close,以关闭Add Items to the Project。 图2.8 新的设计文件LED_FLOW.v 4. 双击打开LED_FLOW.v文件(注意:若是Verilog文件已经关联了其他的文本编辑器,则双击后在关联的文本编辑器中打开)。 图2.9 LED_FLOW代码输入窗口 在LED_FLOW.v输入下面的测试平台代码:

Modelsim使用常见问题及解决办法

Modelsim使用常见问题及解决办法 在ISE启动modelsim时遇到问题 1。我在ISE中启动modelsim时出现了下面的错误 Loading work.tb_ic1_func # ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver". # No such file or directory. (errno = ENOENT) # ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT) # Loading work.fifoctlr_ic_v2 # ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver". # No such file or directory. (errno = ENOENT) # ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT) # ** Error: (vsim-3033) fifoctlr_ic_v2.v(126): Instantiation of 'BUFGP' failed. The design unit was not found. 是什么原因? “点到仿真模式,在source里面选中你建立工程选择的芯片,然后看Processes,点开,有个compile HDL simulation library,运行一下就OK了” 2.ISE用modelsim仿真提示:# ** Error: (vish-4014) No objects found matching '*'.结果仿真时老是报错: # ** Error: (vish-4014) No objects found matching '*'. # Error in macro ./test_top_tb.fdo line 10 # (vish-4014) No objects found matching '*'. # while executing # "add wave *" 解决办法,改modelsim.ini文件中的一个参数:VoptFlow = 0 # ** Error: (vish-4014) No objects found matching 'XXXX'. 在之前的设计里有一个信号XX, 并且保持在wave.do文件里 现在这个信号在你的设计你被去掉了,modelsim仍然调用旧的wave.do,找不到对应的信号XX, 就报错误这个错误可以忽略 3.当对IP核修改后,用Modelsim仿真显示:No entity is bound for inst 或CE is not in the entity。(CE是改动后添加的一个管脚),从而仿真无结果。 解决办法:首先选中该IP核的.xco文件点击右键->属性将属性改为"Synthesis/Imp + Simulation." 然后将其对应的.v或.vhd文件的属性也改为"Synthesis/Imp + Simulation." 4.启动modelsim后,没有出错,但是有warning:(vsim-3009) [TSCALE] - Module 'ODDR' does not have a `timescale directive in effect, but previous modules do.输入信号均正确,调用的IP core或原语的输出为高阻态。

modelsim仿真必会教程

Modelsim功能仿真新手教程 By wangjun850725@https://www.sodocs.net/doc/9a7429317.html, 操作系统:win7 软件版本:modelsim6.5se 本文只针对初学者,让他们少走点弯路,modelsim软件本身感觉还是比较难以使用的。本人才疏学浅,但有颗助人的心。大神请跳过,不要鄙视我。 如有错误,请不吝指点。 QQ群:41143927 建立工程 省略N字,这没有什么好说的。几乎所有的软件都是以工程为基础的。 添加设计文件 因为我已经编辑好了文件,所以直接添加已经存在的。没有人会用modelsim自带的编辑器来写程序(要是没有选择,我宁愿用记事本,如果你用了,我佩服你)。 编译文件 没有什么好说的,添加进去的文件全部编译就好了。 如果你看编译后的文件后面还有一个问号,你不爽,鼠标右键更新下就好了 开始仿真 Modelsim se版本是可以手动描绘激励波形的,但这种方法太笨,太烦,修改起来很不方便,所以直接放弃。

Simulate里有个start simulate,点开 这里有几点要说明下 1.要点开work库,找到你testbench对应的那个模块 2.Resolution选不选关系不大,如果你设计文件指定了仿真时间的话 3.Optimization,要把这个勾去掉,不然会优化掉很多信号,这里也坑了我很久。 功能仿真只要这么多,如果做后仿,library里要添加已经编译好的器件库,SDF里要添加.vo,.sdo文件 观察波形 添加信号到波形窗口的方法有很多,刚学手动添加,后来肯定是要在脚本里指定的,下面会有 首先要把设计中的信号添加到wave窗口里。

鼠标左键按住不放,将对应的模块拖到wave窗口里,这是最简单的办法。 如果设计的模块多了,每个模块的信号不能很好的被区分,就可以在每个模块的中间插入一个Divider,信号旁边右键就可以看到,最好给起个名字 如果你的模块层次非常的多,信号的路径名字就会占据本来就不大的屏幕时很不爽的。 菜单Wave‐>Wave preference‐>Display signal path里面改成1就可以了 运行仿真 在Transcript窗口里输入 Run 1ms 搞定,波形神马的就出现了。你要做的工作就是看波形是否是你想要的。

有关modelsim的问题汇总

问题一:编译xilinx仿真库 在网上搜了无数帖子,结合自己数小时的实践,终于搞定了Xilinx仿真库。 测试环境:Windows XP3,Xilinx ISE Suite 10.1,ModelSim SE 6.5c 使用ISE自带的库生成工具是最方便的方法。 首先打开ISE,在Edit->Preferences...->ISE General 的Intergrated Tools 的Model Tech Simulator中指定Modelsim.exe的实际安装路径。(在这里我的路径是D:\Work\modeltech_6.5c\win32\modelsim.exe,请根据自己的实际情况更改)。OK以后退出ISE。 然后到ModelSim安装目录下找到ModelSim.ini文件,右键将其只读属性去掉,确定。 按下WIN+R,输入compxlibgui后回车,这其实就是自带的工具Simulation Library Compilation Wizard。点击Select simulator,选中ModelSim。检查路径正确了以后选Next。再Next,建议再Next,或者根据自己的实际需要选择FPGA/CPLD的具体型号。继续Next,在Map only to existing pre-compiled libraries前打上勾,在Output Directory for modelsim.ini file using mapped libraries中选择modelsim安装根目录modelsim.ini所在的路径,这一步很重要。再点击Next就开始编译了。 最后把ModelSim.ini文件的只读属性改回去,万事OK…… 问题二: Hello all, Whenever I need to look at a filter output (or any DSP core), I used to define a real signal and assign it to what I want to examine, roughly something like this: dac_real_out <= hex2real(dac_holder, 12.0); where dac_holder is a std_logic_vector. It is much easier to look at an analogue signal waveform instead of tracing hex values word by word. This used to work quite alright using ModelSim XE edition. Now for some reason, it seems I can't get it to compile my design---I get the following error: # ** Error: (vcom-42) Unsupported ModelSim library format for "work". (Format: 3) My first question is: can I go around it as I've never encountered this before.

相关文档

- Modelsim 仿真步骤总结

- ModelsimSE仿真步骤

- ModelSim仿真软件使用

- Modelsim仿真详细教程

- modelsim使用 + 前仿真 + 后仿真 + verilog

- 使用Quartus-Modelsim联合仿真

- Quartus调用ModelSim仿真教程

- ModelSim的前后仿真(Quartus)

- ModelSim Verilog仿真实例附程序

- modelsim仿真详细过程

- ModelSim软件仿真步骤教程

- Quartus+ModelSim-Altera 联合仿真(Verilog版)

- ModelSim后仿真

- 使用Modelsim仿真FPGA工程步骤以及一些问题

- vivado用modelsim仿真

- Modelsim仿真步骤

- 基于Modelsim的功能仿真

- ISE和Modelsim联合仿真_修订版

- Quartus_ii_11.0教程(包含modelsim仿真)

- ModelSim入门指导答辩