4线-2线优先编码器

4线-2线优先编码器设计、仿真与实现1.真值表:

2.逻辑关系

Y1 = X0 + X1

Y2 = X0 + X1’X2

3.Verolig 代码实现

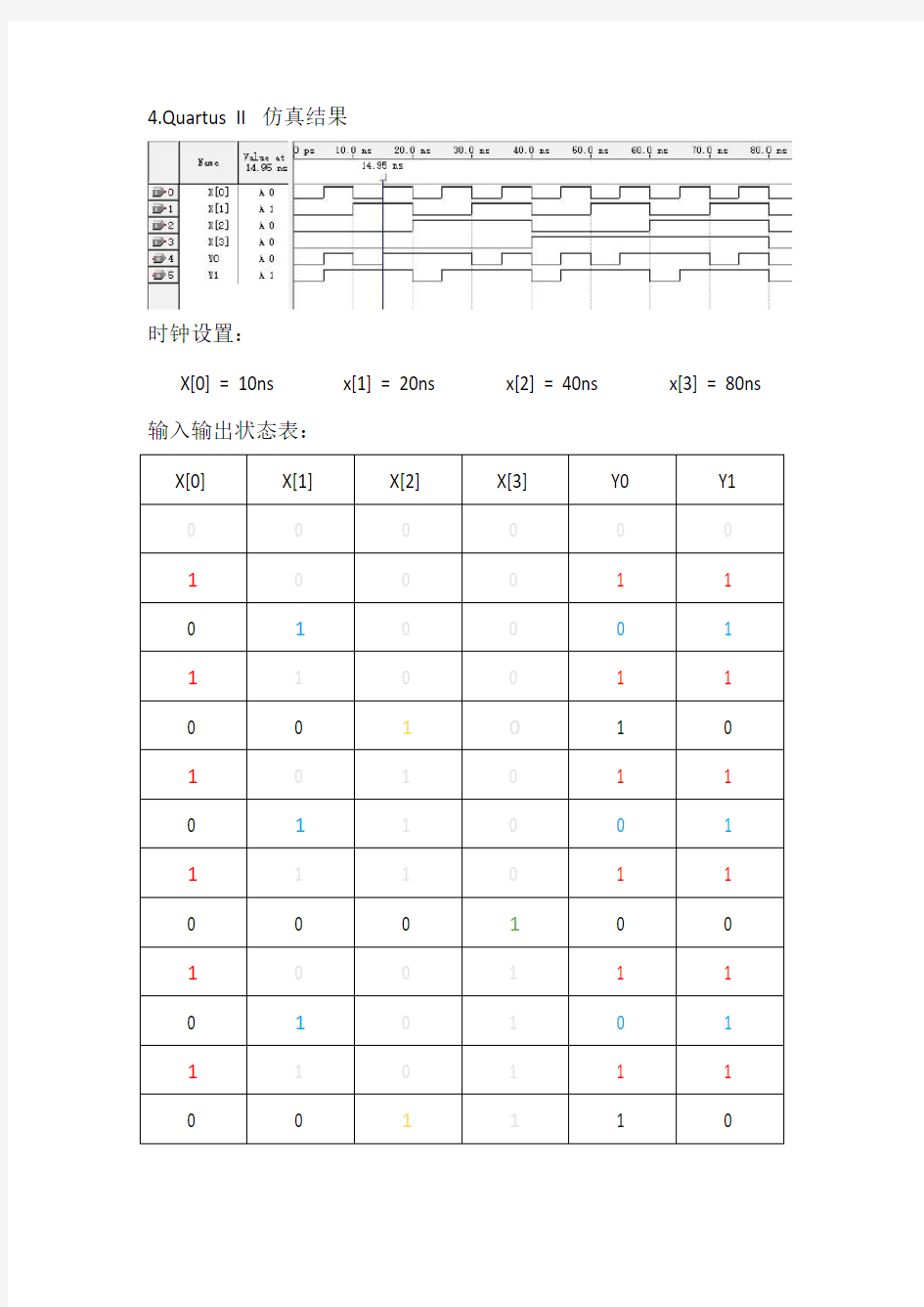

4.Quartus II 仿真结果

时钟设置:

X[0] = 10ns x[1] = 20ns x[2] = 40ns x[3] = 80ns 输入输出状态表:

5.FPGA引脚设置

优先编码器74LS148

优先编码器74LS148 有些单片机控制系统和数字电路中,无法对几个按钮的同时响应做出反映,如电梯控制系统在这种情况下就出出现错误,这是绝对不允许的于是就出现了74ls148优先编码器,先说一下他的基本原理.他允许同时输入两个以上编码信号。不过在设计优先编码器时已经将所有的输入信号按优先顺序排了队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。 〈74ls148管脚功能〉〈74ls148引脚图〉 74ls148优先编码器管脚功能介绍:为16脚的集成芯片,电源是VCC(16) GND(8),I0—I7为输入信号,A2,A1,A0为三位二进制编码输出信号,IE是使能输入端,OE是使能输出端,GS 为片优先编码输出端。 〈74ls148逻辑图〉〈74ls148逻辑表达式〉 使能端OE(芯片是否启用)的逻辑方程: OE =I0·I1·I2·I3·I4·I5·67·IE 当OE输入IE=1时,禁止编码、输出(反码):A2,A1,A0为全1。 当OE输入IE=0时,允许编码,在I0~I7输入中,输入I7优先级最高,其余依次为:

I6,I5,I4,I3,I2,I0,I0等级排列。 输入输出 EI I0I1I2I3I4I5I6I7A2A1A0GS EO 1 x x x x x x x x 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 x x x x x x x 0 0 0 0 0 1 0 x x x x x x 0 1 0 0 1 1 0 0 x x x x x 0 1 1 0 1 0 1 0 0 x x x x 0 1 1 1 0 1 1 1 0 0 x x x 0 1 1 1 1 1 0 0 1 0 0 x x 0 1 1 1 1 1 1 0 1 1 0 0 x 0 1 1 1 1 1 1 1 1 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 <优先编码器74ls148功能表> 从以上的的功能表中可以得出,74ls148输入端优先级别的次序依次为I7,I6,…,I0 。当某一输入端有低电平输入,且比它优先级别高的输入端没有低电平输入时,输出端才输出相应该输入端的代码。例如:I5=0且I6=I7=1(I6、I7优先级别高于I5) 则此时输出代码010 (为(5)10=(101)2的反码)这就是优先编码器的工作原理。

编码器计数的接线方法

15. 各种输出形式的旋转编码器与后续设备(PLC、计数器等)接线分别怎么接? ⑴与PLC连接,以CPM1A为例①NPN集电极开路输出 方法1:如下图所示 这种接线方式应用于当传感器的工作电压与PLC的输入电压不同时,取编码器晶体管部分,另外串入电源,以无电压形式接入PLC。但是需要注意的是,外接电源的电压必须在DC30V 以下,开关容量每相35mA以下,超过这个工作电压,则编码器内部可能会发生损坏。 具体接线方式如下:编码器的褐线接编码器工作电压正极,蓝线接编码器工作电压负极,输出线依次接入PLC的输入点,蓝线接外接电源负极,外接电源正极接入PLC的输入com端。 方法2:编码器的褐线接电源正极,输出线依次接入PLC的输入点,蓝线接电源负极,再从电源正极端拉根线接入PLC输入com端。 ②电压输出接线方式如图所示: 具体接线方式如下:编码器的褐线接电源正极,输出线依次接入PLC 的输入点,蓝线接电源负极,再从电源正极端拉根线接入PLC输入com端。不过需要注意的是,不能以下图方式接线。 ③PNP集电极开路输出 接线方式如下图所示:

具体接线方式如下:编码器的褐线接工作电压正极,蓝线接工作电压负极,输出线依次接入PLC的输入com端,再从电源负极端拉根线接入PLC的输入com端。④线性驱动输出具体接线如下:输出线依次接入后续设备相应的输入点,褐线接工作电压的正极,蓝线接工作电压的负极。 ⑵与计数器连接,以H7CX(OMRON制)为例H7CX输入信号分为无电压输入和电压输入。 ①无电压输入:以无电压方式输入时,只接受NPN输出信号。 NPN集电极开路输出的接线方式如下: 具体接线方式如下:褐线接电源正极,蓝线接电源负极,再从电源负极端拉根线接6号端子,黑线和白线接入8和9号端子,如果需要自动复位,则橙线接入7号端子。 NPN电压输出的接线方式如下: 接线方式与NPN集电极开路输出方式一样。 ②电压输入NPN集电极开路输出的接线方式如下图所示: 具体接线方式如下:褐线接电源正极,蓝线接电源负极,再从电源负极端拉根线接6号端子,黑线和白线接入8和9号端子,如果需要自动复位,则橙线接入7号端子。PNP集电极开

74ls148优先编码器

实验六编码、译码显示电路 一、实验目的 1.熟悉七段发光二极管显示器的结构及工作原理。 2.掌握分段式显示译码电路的设计方法及调试方法。 3.掌握编码器的逻辑功能及其应用。 4.掌握中规模显示译码器74LS48和优先编码器74LS148的功能和使用方法。 二、手动实验预习要求及思考题 1.复习8/3线优先编码器74LS148的工作原理及逻辑功能。 2.复习中规模译码器74LS48的工作原理及逻辑功能。 3.用发光二极管组成的七段显示器按结构分为共阴极和共阳极两种,中规模译码器74LS48应采用哪种结构形式?为什么? 4.译码电路输出与笔画段之间是否要加限流电阻器。 5.设计一个能显示0、一、二、三,四个字形的译码逻辑电路,输入两变量A、B。 三、仿真实验要求 采用EWB或者PSpice软件仿真电路,以便将仿真结果与实验结果进行比较。 四、实验仪器及器件 1.TTL集成芯片若干 2.万用表一块 3.电子学综合实验装置一台 五、实验内容与步骤 1.七段显示译码器的设计和调试 选用共阴极数码管、与非门74LS00、反相器74LS04和510?限流电阻,根据预习中设计出的能显示0、一、二、三,四个字形的译码逻辑电路连好,调试电路,到数码管能显示0、一、二、三,四个字形为止。要求写出设计过程,列出真值表,写出逻辑表达式,画出逻辑图。 选做:设计一个译码器,输入为两个变量,输出能显示出数字0~9和字母AbCdEFHP 中任四个字形。 2.测试74LS48译码逻辑功能 74LS48的各管脚的功能为: (1)试灯输入:当将LT置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。 (2)灭灯输入:当将BI置成低电平时,不论A、B、C、D输入状态如何,记录显示器状态。 (3)灭零输入:在A、B、C、D均为低电平时,把_____ RBI端分别接高电平、低电平,观 察数码管显示情况。

编码器接线规范

编码器接线规范 编码器(encoder)是将物理信号编制、转换为可用以通讯、传输和存储的信号的一种设备。应用于速度控制或位置控制系统的检测元件。现场运输小车均使用的是帝尔TR 厂家的CEV65 M 型号编码器,其中C 表示紧凑绝对型、E 表示光学、V 表示实轴、M 表示多圈、65表示外壳 65mm。 图1编码器 图2 编码器后盖地址设定及接线端子介绍

编码器接线方法1: 所需工具:剥线刀、开口2mm一字改锥、内六花一套、偏口钳一把,开口3mm十字螺丝刀一把。 操作步骤: 1)设定地址,接线口朝下拿编码器,左边拨码是十位,右边拨码是个位。 2)设定终端:只接入线时,此编码器是终端,两个终端都打到ON;入线和出线都接时两个拨码都拨到1位。 3)接线: a)把接线端子的附件按顺序套在DP线上,如图3; 图3接线附属设备安装顺序 b)剥除DP线外层的橡胶层10cm左右,如图4; 图4 DP线拨线图5处理屏蔽线 c)把内层的金属屏蔽层屡开,并拧成一股,如图5; d)剥开线内部白色保护层,把屏蔽层接到图7中椭圆标出的螺丝上, 并接网线,A接绿线,B接红线,如图6,图7。

图6穿线图7接线 此方法优、缺点: 优点:屏蔽层接触好; 缺点:接线方法复杂,不易于操作 编码器接线方法2: 所需工具:DP线剥线刀、开口2mm一字改锥、内六花一套、偏口钳一把,开口3mm十字螺丝刀一把。 操作步骤: 1)设定地址,接线口朝下拿编码器,左边拨码是十位,右边拨码是个位。 2)设定终端:只接入线时,此编码器是终端,两个终端都打到ON;入线和出线都接时两个拨码都拨到1位。 3)接线: a)用专业DP线剥线刀剥线,按图8按顺序穿上附件,并做好屏蔽; 图8剥线图9穿线 b)接线,A接绿线,B接红线,如图10。

用74ls148和逻辑门电路实现16:4线优先编码器

实验三 MSI(中规模集成组合电路)应用 一、实验目的 1、掌握MSI芯片引脚图、功能表、原理图等查阅方法; 2、掌握MSI独立芯片的功能的测试与理解; 3、用MSI的设计与实现组合电路综合功能; 4、体会MSI与门电路的区别; 二、实验使用的器件和设备 四2输入与门74LS08 1片 8线-3线优先编码器74LS148 2片 TDS-4数字系统综合实验平台 2台 三、实验题目 用74LS148和逻辑门电路实现16:4线优先编码器。 四、实验过程 1、选择实验题目,分析逻辑功能 用74LS148和逻辑门电路实现16:4线优先编码器。 逻辑功能:按优先顺序从级别最高的输入信号编码,当多个输入同时有效时,只对其中优先 级别最高的输入信号编码,而对级别较低的输入信号不予理睬。 2、根据逻辑功能写出真值表 输入输出 I7 I8 I9 I10 I11 I12 I13 I14 I15 A B C GS D EO EI I0 I1 I2 I3 I4 I5 I6 1 X X X X X X X X X X X X X X X X 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 X X X X X X X X X X X X X X X 0 0 0 0 1 0 1 0 X X X X X X X X X X X X X X 0 1 0 0 1 1 0 1 0 X X X X X X X X X X X X X 0 1 1 0 1 0 1 0 1 0 X X X X X X X X X X X X 0 1 1 1 0 1 1 1 0 1 0 X X X X X X X X X X X 0 1 1 1 1 1 0 0 1 0 1 0 X X X X X X X X X X 0 1 1 1 1 1 1 0 1 1 0 1 0 X X X X X X X X X 0 1 1 1 1 1 1 1 1 0 1 0 1 0 X X X X X X X X 0 1 1 1 1 1 1 1 1 1 1 1 0 1 0 X X X X X X X 0 1 1 1 1 1 1 1 1 0 0 0 0 0 1

优先编码器课程设计

东北石油大学课程设计任务书 课程硬件课程设计 题目 8-3优先级编码器设计 专业计算机科学与技术姓名学号 主要内容、基本要求等 一、主要内容: 利用EL教学实验箱、微机和QuartusⅡ软件系统,使用VHDL语言输入方法设计8-3优先编码器。可以利用层次设计方法和VHDL语言,完成硬件设计设计和仿真。最后在EL教学实验箱中实现。 二、基本要求: 设计并实现一个8-3优先级编码器,要求I0优先级最高,I7优先级最低,编码输出为原码。 三、扩展要求: 输入端加使能端,在使能端为有效的低电平时,进行编码;在使能端为无效的高电平时,输出高阻状态。 四、参考文献: [1] 杨刚,龙海燕.现代电子技术-VHDL与数据系统设计.北京:电子工业出版 社,2004 [2] 黄仁欣.EDA技术实用教程.北京:清华大学出版社,2006 [3] 潘松.VHDL实用教程[M].成都:电子科技大学出版社,2000 [4] 李国丽,朱维勇.电子技术实验指导书.合肥:中国科技大学出版社,2000[5] 宋振辉. EDA技术与VHDL.北京:北京大学出版社,2008 完成期限18-19周 指导教师张岩 专业负责人富宇 2011年6月28日

目录 第1章概述 (1) 1.1 EDA的概念 (1) 1.2 EDA技术及应用 (2) 1.3 EDA技术发展趋势 (2) 1.4 Quartus II特点介绍 (3) 第2章硬件描述语言——VHDL (4) 2.1 VHDL的简介 (4) 2.2 VHDL语言的特点 (4) 2.3 VHDL的设计流程 (5) 第3章 8-3优先编码器的设计 (6) 3.1 编码器的工作原理 (6) 3.2 8-3优先编码器的设计 (6) 3.3 8-3优先编码器仿真及分析 (7) 3.4 在实验箱上实现8-3优先编码器 (8) 结论 (11) 参考文献 (12)

数字电路-2进制优先编码器

数字电路实验报告 姓名:陈小龙学号:14051113 班级: 专业:网络工程课程名称:数字电路设计 任课老师:张怀相实验名称:2进制优先编码器1.实验程序源代码 module cxl_4(IN,Y,EN,DONE); input[7:0] IN; input EN; output DONE; output[2:0] Y; reg DONE; reg[2:0] Y; always @(*) begin if(!EN) begin if(IN[0]==1) begin Y=3'b000; DONE=1; end

else if(IN[0]==0&&IN[1]==1) begin Y=3'b001; DONE=1; end else if(IN[0]==0&&IN[1]==0&&IN[2]==1) begin Y=3'b010; DONE=1; end else if(IN[0]==0&&IN[1]==0&&IN[2]==0&&IN[3]==1) begin Y=3'b011; DONE=1; end else if(IN[0]==0&&IN[1]==0&&IN[2]==0&&IN[3]==0&&IN[4]== 1) begin Y=3'b100; DONE=1;

end else if(IN[0]==0&&IN[1]==0&&IN[2]==0&&IN[3]==0&&IN[4]== 0&&IN[5]==1) begin Y=3'b101; DONE=1; end else if(IN[0]==0&&IN[1]==0&&IN[2]==0&&IN[3]==0&&IN[4]== 0&&IN[5]==0&&IN[6]==1) begin Y=3'b110; DONE=1; end else if(IN[7]==1&&IN[6]==0&&IN[5]==0&&IN[4]==0&&IN[3]== 0&&IN[2]==0&&IN[1]==0&&IN[0]==0) begin Y=3'b111; DONE=1; end

编码器的选型及技术解答

编码器的选型及技术解答 一、问:增量旋转编码器选型有哪些注意事项? 应注意三方面的参数: 1.机械安装尺寸,包括定位止口,轴径,安装孔位;电缆出线方式;安装空间体积;工作环境防护等级是否满足要求。 2.分辨率,即编码器工作时每圈输出的脉冲数,是否满足设计使用精度要求。 3.电气接口,编码器输出方式常见有推拉输出(F型HTL格式),电压输出(E),集电极开路(C,常见C为NPN型管输出,C2为PNP型管输出),长线驱动器输出。其输出方式应和其控制系统的接口电路相匹配。 二、问:请教如何使用增量编码器? 1,增量型旋转编码器有分辨率的差异,使用每圈产生的脉冲数来计量,数目从6到5400或更高,脉冲数越多,分辨率越高;这是选型的重要依据之一。 2,增量型编码器通常有三路信号输出(差分有六路信号):A,B和Z,一般采用TTL电平,A脉冲在前,B 脉冲在后,A,B脉冲相差90度,每圈发出一个Z脉冲,可作为参考机械零位。一般利用A超前B或B超前A进行判向,增量型编码器定义为轴端看编码器顺时针旋转为正转,A超前B为90°,反之逆时针旋转为反转B超前A为90°。也有不相同的,要看产品说明。 3,使用PLC采集数据,可选用高速计数模块;使用工控机采集数据,可选用高速计数板卡;使用单片机采集数据,建议选用带光电耦合器的输入端口。 4,建议B脉冲做顺向(前向)脉冲,A脉冲做逆向(后向)脉冲,Z原点零位脉冲。 5,在电子装臵中设立计数栈。 增量型编码器与绝对型编码器的区分:编码器如以信号原理来分,有增量型编码器,绝对型编码器。 增量型编码器(旋转型)工作原理:由一个中心有轴的光电码盘,其上有环形通、暗的刻线,有光电发射和接收器件读取,获得四组正弦波信号组合成A、B、C、D,每个正弦波相差90度相位差(相对于一个周波为360度),将C、D信号反向,叠加在A、B两相上,可增强稳定信号;另每转输出一个Z相脉冲以代表零位参考位。由于A、B两相相差90度,可通过比较A相在前还是B相在前,以判别编码器的正转与反转,通过零位脉冲,可获得编码器的零位参考位。编码器码盘的材料有玻璃、金属、塑料;玻璃码盘是在玻璃上沉积很薄的刻线,其热稳定性好,精度高。金属码盘直接以通和不通刻线,不易碎,但由于金属有一定的厚度,精度就有限制,其热稳定性就要比玻璃的差一个数量级。塑料码盘是经济型的,其成本低,但精度、热稳定性、寿命均要差一些。 分辨率:编码器以每旋转360度提供多少的通或暗刻线称为分辨率,也称解析分度、或直接称多少线,一般在每转分度5~10000线。 信号输出:信号输出有正弦波(电流或电压),方波(TTL、HTL),集电极开路(PNP、NPN),推拉式多种形式,其中TTL为长线差分驱动(对称A,A-;B,B-;Z,Z-),HTL也称推拉式、推挽式输出,编码器的信号接收设备接口应与编码器对应。 信号连接:编码器的脉冲信号一般连接计数器、PLC、计算机,PLC和计算机连接的模块有低速模块与高速模块之分,开关频率有低有高。如单相联接,用于单方向计数,单方向测速。A.B两相联接,用于正反向计数、判断正反向和测速。A、B、Z三相联接,用于带参考位修正的位臵测量。A、A-,B、B-,Z、Z-连接,

编码器控制线制作及连接

编码器控制云台的控制线连接图 一、D31摄像头的控制 方法一: 线缆制作: RJ45(网线)接口:直连线做法(白橙、橙、白绿、蓝、白蓝、 绿、白棕、棕) Com口做法:焊接2(白绿)、3(橙)、5(白棕)口 线缆连接: RJ45直接接在编码器的485口上,Com口直接接D31的控制线,不用485转232的转换头 注:此方法不能做为工程安装使用 方法二:

线缆制作: a)网线一端为水晶头(568B线序),将网线另一端颜色为橙白(485+) 和橙(485-)的线缆剥出。 b)DB9(公)到DB9(公)转接线:用双芯线将两个DB9头的2、3 脚线交叉连接,两芯线的屏蔽线将两DB9的第五根5脚线直连。 c)DB9(母)到VISCA(公)为成品线。 线缆连接: 将网线水晶头一端接到监控前端的RS485口,另一端颜色为橙白(485+)、橙(485-)分别接到485转换器的485+(T/R+)、485-(T/R-),对应关系为+对+,-对-;然后将485转换器的232接口接到DB9转接线上,再将DB9转接线另一端接到DB9(母)到VISCA(公)成品线的DB9端,然后将VISCA端接到SONYD100的VISCA口即可。 如果编码器的485口是用端子连接的话,就把网线的水晶头去掉,白橙接+橙接—,即可实现云台控制。 注:如果云台无法控制的话,把485的+—对调一下即可。二、高速球的云台控制 大多数高速快球的控制线为485接口,在连接控制线时,只需用两芯屏蔽线或网线进行连接。 1.当两端都是485接口时,用两芯屏蔽线按照+接+、—接—连 接。 2.一端为485接口,另一端为RJ45口,用高速球的+、—连接

组合电路的VHDL设计优先编码器编码器-Read

组合电路的VHDL设计 优先编码器 编码器(encoder)也属于码制转换器一类 (BCD—1-out-of-10)( p.49 表2-9 ) 优先编码器属于多对1转换关系,没有一一对应关系,难以采用上述方式描述; 74148 优先编码器真值表见p.278 表5-23,表中含有大量‘x’项,目前VHDL还不能直接对其进行运算处理; 在p.384 表5-26中,显示了行为设计的一种形式:采用for-loop语句; 也可以采用数据流设计中的条件代入语句实现: 例:简化74148优先编码器的数据流设计 数据输入 i[7..0] 低电平有效控制输入el 低电平有效数据输出a[2..0] 反函数输出 library ieee; use ieee.std_logic_1164.all; entity kencoder is port (i: in std_logic_vector (7 downto 0); el: in std_logic; a: out std_logic_vector(2 downto 0)); end kencoder; architecture rtl of kencoder is signal a1:std_logic_vector(2 downto 0);

begin a1 <="000" when i(7)= '0' else "001" when i(7 downto 6)="10" else "010" when i(7 downto 5)="110" else "011" when i(7 downto 4)="1110" else "100" when i(7 downto 3)="11110" else "101" when i(7 downto 2)="111110" else "110" when i(7 downto 1)="1111110" else "111"; a<=a1 when el='0' else "111"; end rtl; 奇偶校验电路 parity checker 奇偶校验电路是实现数据错误检验的一种基本电路,其方式是检测在9位输入数据中‘1’的个数是奇数还是偶数; 3输入端异或门可以看作3位奇偶校验电路: ‘1’的个数为奇数时输出为‘1’,为偶数时输出为‘0’; 利用该电路可以构成9位奇偶校验电路; p.418 表5-47 9位奇偶校验电路的行为设计 p.419 表5-48 9位奇偶校验电路的结构设计 例 9位奇偶校验电路的数据流设计 library ieee; use ieee.std_logic_1164.all;

欧姆龙编码器正确的接线

(1)正确接线至关重要,如图1 为NPN 输出增量型E6B2-CWZ6C 的接线原理,图2 为NPN 输出增量型E6B2-CWZ6C 的实际接线,棕色线接电源正极,蓝色线接电源负极,黑色线接输入0.00,白色线接输入0.01,橙色线接输入0.04,PLC 的COM 接电源正极。 (2)下图为PNP 输出增量型E6B2-CWZ6B 的实际接线图,棕色线接电源正极,蓝色线接电源负极,黑色线接输入0.00,白色线接输入0.01,橙色线接输入0.04,PLC 的COM 接电源负极。

(3)图1 为绝对值型编码器的线与PLC 输入的点的对应图,图2 为NPN 输出绝对值型 E6C3-AG5C 的实际接线图,红色线接电源正极,黑色线接电源负极,褐色线接输入0.00,橙色线接输入0.01,黄色线接输入0.02,绿色线接输入0.03,蓝色线接输入0.04,紫色线接输入0.05,灰色线接输入0.06,白色线接输入0.07,粉色线接输入0.08,PLC 的COM 接电源正极。

(4)下图为PNP 输出绝对值型E6C3-AG5B 的实际接线图,红色线接电源正极,黑色线接 电源负极,褐色线接输入0.00,橙色线接输入0.01,黄色线接输入0.02,绿色线接输入0.03,蓝色线接输入0.04,紫色线接输入0.05,灰色线接输入0.06,白色线接输入0.07,粉色线接 输入0.08,PLC 的COM 接电源负极。 (5)图1 为线驱动编码器的接线原理,图2 为实际接线图,黑色线接A0+,黑红镶边线A0-,白色线接B0+,白红镶边线接B0- 橙色线接Z0+,橙红镶边线接Z0-,褐色线接电源+5V,蓝色线接电源0V,切勿接线错误。

优先编码器课程设计

优先编码器课程设计 IMB standardization office【IMB 5AB- IMBK 08- IMB 2C】

东北石油大学课程设计任务书 课程硬件课程设计 题目8-3优先级编码器设计 专业计算机科学与技术姓名学号 主要内容、基本要求等 一、主要内容: 利用EL教学实验箱、微机和QuartusⅡ软件系统,使用VHDL语言输入方 法设计8-3优先编码器。可以利用层次设计方法和VHDL语言,完成硬件设计设计和仿真。最后在EL教学实验箱中实现。 二、基本要求: 设计并实现一个8-3优先级编码器,要求I0优先级最高,I7优先级最 低,编码输出为原码。 三、扩展要求: 输入端加使能端,在使能端为有效的低电平时,进行编码;在使能端为无效的高电平时,输出高阻状态。 四、参考文献: [1]杨刚,龙海燕.现代电子技术-VHDL与数据系统设计.北京:电子工业出版 社,2004 [2] 黄仁欣.EDA技术实用教程.北京:清华大学出版社,2006 [3]潘松.VHDL实用教程[M].成都:电子科技大学出版社,2000 [4]李国丽,朱维勇.电子技术实验指导书.合肥:中国科技大学出版社,2000[5]宋振辉.EDA技术与VHDL.北京:北京大学出版社,2008 完成期限18-19周 指导教师张岩 专业负责人富宇

2011年 6月28日 目录 第1章概述 1.1EDA的概念 EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB 版图的整个过程在计算机上自动处理完成。现在对EDA的概念或范畴用得很宽。包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。EDA设计可分为系统 级、电路级和物理实现级。 EDA是电子技术设计自动化,也就是能够帮助人们设计电子电路或系统的软件工具。该工具可以在电子产品的各个设计阶段发挥作用,使设计更复杂的电路和系统成为可能。在原理图设计阶段,可以使用EDA中的仿真工具论证设计的正确性;在芯片设计阶段,可以使用EDA中的芯片设计工

4线2线优先编码器设计

4线2线优先编码器设计 自动化1005班吴国鹏 U201013735 一、设计要求: 1、设计一个4线2线优先编码器,其功能如P285表9.43所示。 2、用实验板上的发光二极管或译码显示电路显示结果。 二、设计分析: 1、优先编码器:允许同时输入两个以上的有效编码信号。当同时输入几个有效编码信号时,优先编码器能按预先设定的优先级别,只对其中优先权最高的一个进行编码。 2、二进制编码器的结构框图 3、4线-2线优先编码器―――根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先级别。识别这类请求信号的优先级别并进行编码的逻辑部件称为优先编码器。 4线-2线优先编码器的功能表如下: 、 三、源代码 module A4_TO_2(in_I,out_A); input [3:0] in_I; output [1:0] out_A;

reg [1:0] out_A; always @(in_I) begin case(in_I) 4'b0001 : out_A=2'b00; 4'b0010 : out_A=2'b01; 4'b0011 : out_A=2'b01; 4'b0100 : out_A=2'b10; 4'b0101 : out_A=2'b10; 4'b0110 : out_A=2'b10; 4'b0111 : out_A=2'b10; 4'b1000 : out_A=2'b11; 4'b1001 : out_A=2'b11; 4'b1010 : out_A=2'b11; 4'b1011 : out_A=2'b11; 4'b1100 : out_A=2'b11; 4'b1101 : out_A=2'b11; 4'b1110 : out_A=2'b11; 4'b1111 : out_A=2'b11; endcase end endmodule 四、仿真波形

实验三-8线3线优先编码器

姓名学号实验日期成绩 XXX XXXXXXX年月日 实验三基本组合逻辑电路的PLD实现(2) ●实验名称:利用原理图输入法与VerilogHDL输入法设计一个8线-3线优先编码器 ●实验目的: 1.熟悉用可编程器件实现基本组合逻辑电路的方法。 2.进一步熟悉MAX+plus II软件的使用方法,熟悉原理图输入法和VerilogHDL输入法, 进一步熟悉如何编译,器件选择,管脚分配和仿真。 ●预习要求: 1.回顾数字电路中关于优先编码器的相关知识。 ●实验说明: 1.用MAX+plus II软件开发PLD器件有两种设计输入方式:原理图输入和HDL语言输 入方式,或者将两者结合起来,一部分电路采用原理图,另一部分采用HDL语言。 2.优先编码器的功能是允许同时在几个输入端有输入信号,编码器按照输入信号的优 先等级对同时输入的多路信号中优先级最高的一路进行编码。 3.8线-3线优先编码器的真值表如下图所示: ●实验内容与步骤: 1.新建一个属于自己的工程目录。 2.新建一张电路图文档,调用8线-3线优先编码器芯片74148(注意其均是低电平有 效),完成设计。 3.对电路图进行编译,仿真。 4.用VerilogHDL语言方式编写一个8线-3线优先编码器。 5.完成编译,管脚分配,并对模块进行仿真。 ●实验报告要求: 1.将自己绘制的电路图或者编写的VerilogHDL代码,截图或者复制到实验报告中。 2.将代码关键位置写上相应注释(可用中文)。 3.对仿真波形截图,贴到实验报告中。 ●实验图表与数据: 1. 8线-3线优先编码器电路图:

2. 8线-3线优先编码器电路仿真波形: 3 .8线-3线优先编码器Verilog代码:

编码器PLC接线

旋转编码器与后续设备(PLC、计数器等)接线如何接? 分享到: ⑴与PLC连接,以CPM1A为例: ①NPN集电极开路输出 方法1:如下图所示 这种接线方式应用于当传感器的工作电压与PLC的输入电压不同时,取编码器晶体管部分,另外串入电源,以无电压形式接入PLC。但是需要注意的是,外接电源的电压必须在DC30V以下,开关容量每相35mA以下,超过这个工作电压,则编码器内部可能会发生损坏。 具体接线方式如下:编码器的褐线接编码器工作电压正极,蓝线接编码器工作电压负极,输出线依次接入PLC的输入点,蓝线接外接电源负极,外接电源正极接入PLC的输入com 端。 方法2:

编码器的褐线接电源正极,输出线依次接入PLC的输入点,蓝线接电源负极,再从电源正极端拉根线接入PLC输入com端。 ②电压输出 接线方式如图所示: 具体接线方式如下:编码器的褐线接电源正极,输出线依次接入PLC的输入点,蓝线接电源负极,再从电源正极端拉根线接入PLC输入com端。 ③PNP集电极开路输出 接线方式如下图所示: 具体接线方式如下:编码器的褐线接工作电压正极,蓝线接工作电压负极,输出线依次接入PLC的输入com端,再从电源负极端拉根线接入PLC的输入com端。 ④线性驱动输出 具体接线如下:输出线依次接入后续设备相应的输入点,褐线接工作电压的正极,蓝线接工作电压的负极。 ⑵与计数器连接,以H7CX(OMRON制)为例

H7CX输入信号分为无电压输入和电压输入。 ①无电压输入: 以无电压方式输入时,只接受NPN输出信号。 NPN集电极开路输出的接线方式如下: 具体接线方式如下:褐线接电源正极,蓝线接电源负极,再从电源负极端拉根线接6号端子,黑线和白线接入8和9号端子,如果需要自动复位,则橙线接入7号端子。 NPN电压输出的接线方式如下: 接线方式与NPN集电极开路输出方式一样。 ②电压输入 NPN集电极开路输出的接线方式如下图所示:

实验三-8线3线优先编码器

实验三基本组合逻辑电路的PLD实现(2) ●实验名称:利用原理图输入法与VerilogHDL输入法设计一个8线-3线优先编码器 ●实验目的: 1.熟悉用可编程器件实现基本组合逻辑电路的方法。 2.进一步熟悉MAX+plus II软件的使用方法,熟悉原理图输入法和VerilogHDL输入 法,进一步熟悉如何编译,器件选择,管脚分配和仿真。 ●预习要求: 1.回顾数字电路中关于优先编码器的相关知识。 ●实验说明: 1.用MAX+plus II软件开发PLD器件有两种设计输入方式:原理图输入和HDL语言 输入方式,或者将两者结合起来,一部分电路采用原理图,另一部分采用HDL语 言。 2.优先编码器的功能是允许同时在几个输入端有输入信号,编码器按照输入信号的优 先等级对同时输入的多路信号中优先级最高的一路进行编码。 3.8线-3线优先编码器的真值表如下图所示: ●实验内容与步骤: 1.新建一个属于自己的工程目录。 2.新建一张电路图文档,调用8线-3线优先编码器芯片74148(注意其均是低电平有 效),完成设计。 3.对电路图进行编译,仿真。 4.用VerilogHDL语言方式编写一个8线-3线优先编码器。 5.完成编译,管脚分配,并对模块进行仿真。 ●实验报告要求: 1.将自己绘制的电路图或者编写的VerilogHDL代码,截图或者复制到实验报告中。 2.将代码关键位置写上相应注释(可用中文)。 3.对仿真波形截图,贴到实验报告中。 姓名 学号实验日期成绩XXX XXXXXXX 年月日

实验图表与数据: 1. 8线-3线优先编码器电路图: 2. 8线-3线优先编码器电路仿真波形: 3 .8线-3线优先编码器Verilog代码:

实验2-优先编码器

实验3:优先编码器的Verilog HDL描述及仿真 一、实验目的及要求: 1.掌握优先编码器的Verilog HDL描述方法 2.理解逻辑综合的概念 3.掌握RTL电路原理图分析的分析方法 二、实验工具:Quartus_II 9.0 三、实验原理: 1. 优先编码器简介 在数字系统中,常常需要将某一信息变换为某一特定的代码,把二进制代码按一定的规律编排,时每组代码具有一定的含义称为编码。具有编码功能的逻辑电路称之为编码器。常常会有几个部件同时发出服务请求的可能,而在同一时刻只能给其中一个部件发出允许操作信号。因此,必须根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先级别。 8-3优先编码器有8个输入端,3个输出端。还有一个输入使能,输出使能和优先编码器工作状态标志。编码器以低为有效。输入优先级别的次序为7,6,5,…,0。当某一输入端有低电平输入,且比它优先级高的输入没有低电平输入时,输出端才输出相应输入端的代码。优先编码器的真值表如下表1所示。 表1. 2.Verilog程序设计与逻辑综合 2.1 8-3线编码器示例 always @ (din) begin case(din) 8’b0000_0001: dout = 3’b000;

8’b0000_0010: dout = 3’b001; 8’b0000_0100: dout = 3’b010; 8’b0000_1000: dout = 3’b011; … 8’b1000_0000: dout = 3’b111; default : dout = 3’bx; endcase end 2.2 优先编码器设计 优先编码器与上面描述的普通8-3线编码器不同,每次只需判断优先级高的输入端是否有效 always @ (din) begin casex(din) 8’b1xxx_xxxx: dout = 3’b111; 8’b01xx_xxxx: dout = 3’b110; 8’b001x_xxxx: dout = 3’b101; 8’b0001_xxxx: dout = 3’b100; … 8’b0000_0001: dout = 3’b000; default : dout = 3’bx; endcase end 2.3.逻辑综合 逻辑综合是在标准单元库和特定的设计约束的基础上,把设计的高层次描述转换成优化的门级网表的过程。 注意:程序设计方法不同,则逻辑综合得到的RTL原理图不同。 单条的if---else语句综合为一个二选1数据选择器,如程序: module compif (out, d0, d1, s); input d0, d1, s; output out; reg out; always @( s or d0 or d1) if (s) out = d1; else out = d0; endmodule 逻辑综合后的RTL原理图如图2所示。

多路优先编码器

学习活动二 学习活动二:优先编码器电路制作与功能测试

学习目标: 学习目标:

会各数制之间的转换; 能描述优先编码器的编码特点; 会使用8-3线编码器; 能对编码器电路进行功能测试。 建议学时数:10 课时 建议学时数:

生产前准备: 生产前准备:

一、小组成员分工。 班组成员分工,根据学生数量把全班分成 5~6 个班组,每组以 6~8 人 为宜,每组各选一名组长,并分配职责。

小组名称: 序号 1 2 3 4 5 6 姓名 职务

工作理念: 岗位职责

二、小组成员领取面包板及电子元器件并进行登记。

序号 1 2 3

名称

型号

数量

4 5 6 7 8 9 10 11 12

生产过程实施

一、优先编码器功能测试电路框图

电路中加入编码器的作用?知 道什么是二进制代码吗?

二、3 位二进制优先编码器示意图

Y2 Y1 Y0

优先编码器与普通编码器的区

3 位二进制优先编码器

别?

I7 I6

I5

I4 I3 I2 I1

I0

三、8 线-3 线优先编码器 CC4532

VDD

16

Y8 YGS

15 14

I3

13

I2

12

I1

11

I0

10

Y0

9

查找资料理清 CC4532 外引线 引脚排列及各个引脚功能, 最后列出 其功能真值表。

CC4532

1 2 3 4 5 6 7 8

I4

I5

I6

I7

ST

Y2

Y1

VSS

编码器的定义

义项指多义词的不同概念,如李娜的义项:网球运动员、歌手等;非诚勿扰的义项:冯小刚执导电影、江苏卫视交友节目等。查看详细规范>> 编码器(encoder)是将信号(如比特流)或数据进行编制、转换为可用以通讯、传输和存储的信号形式的设备。编码器把角位移或直线位移转换成电信号,前者称为码盘,后者称为码尺。按照读出方式编码器可以分为接触式和非接触式两种;按照工作原理编码器可分为增量式和绝对式两类。增量式编码器是将位移转换成周期性的电信号,再把这个电信号转变成计数脉冲,用脉冲的个数表示位移的大小。绝对式编码器的每一个位置对应一个确定的数字码,因此它的示值只与测量的起始和终止位置有关,而与测量的中间过程无关。 主要分类 编码器可按以下方式来分类。 1、按码盘的刻孔方式不同分类 (1)增量型:就是每转过单位的角度就发出一个脉冲信号(也有发正余弦信号, 编码器(图1)编码器(图1) 然后对其进行细分,斩波出频率更高的脉冲),通常为A相、B相、Z相输出,A 相、B相为相互延迟1/4周期的脉冲输出,根据延迟关系可以区别正反转,而且通过取A相、B相的上升和下降沿可以进行2或4倍频;Z相为单圈脉冲,即每圈发出一个脉冲。 (2)绝对值型:就是对应一圈,每个基准的角度发出一个唯一与该角度对应二进制的数值,通过外部记圈器件可以进行多个位置的记录和测量。 2、按信号的输出类型分为:电压输出、集电极开路输出、推拉互补输出和长线驱动输出。 3、以编码器机械安装形式分类

(1)有轴型:有轴型又可分为夹紧法兰型、同步法兰型和伺服安装型等。 (2)轴套型:轴套型又可分为半空型、全空型和大口径型等。 4、以编码器工作原理可分为:光电式、磁电式和触点电刷式。 工作原理 由一个中心有轴的光电码盘,其上有环形通、暗的刻线, 编码器(图5) 有光电发射和接收器件读取,获得四组正弦波信号组合成A、B、C、D,每个正弦波相差90度相位差(相对于一个周波为360度),将C、D信号反向,叠加在A、B两相上,可增强稳定信号;另每转输出一个Z相脉冲以代表零位参考位。 由于A、B两相相差90度,可通过比较A相在前还是B相在前,以判别编码器的正转与反转,通过零位脉冲,可获得编码器的零位参考位。编码器码盘的材料有玻璃、金属、塑料,玻璃码盘是在玻璃上沉积很薄的刻线,其热稳定性好,精度高,金属码盘直接以通和不通刻线,不易碎,但由于金属有一定的厚度,精度就有限制,其热稳定性就要比玻璃的差一个数量级,塑料码盘是经济型的,其成本低,但精度、热稳定性、寿命均要差一些。 分辨率-编码器以每旋转360度提供多少的通或暗刻线称为分辨率,也称解析分度、或直接称多少线,一般在每转分度5~10000线。 主要作用 它是一种将旋转位移转换成一串数字脉冲信号的旋转式传感器,

优先编码器设计

辽宁工程技术大学 数电项目 设计题目74LS148编码器设计指导教师 院(系、部)电气与控制工程学院 专业班级电网13-1 学号1305080116 姓名苏小平 日期2016/12/23

1.设计规则 在优先编码器电路中,允许同时输入两个以上的编码信号。不过在设计优先编码器时已经将所有的输入信号按照优先顺序依次排序,当几个输入信号同时出现时,只对其中优先级别最高的先进行编码。 2.设计原理 编码器的逻辑功能是将输入的每一个信号编成一个对应的二进制代码。优先编码器的特点是允许编码器同时输入两个以上编码信号 但只对优先级别最高的信号进行编码。 8线-3线优先编码器74LS148有8个信号输入端 输入端为低电平时表示请求编码 为高电平时表示没有编码请求有3个编码输出端 输出3位二进制代码编码器还有一个使能端EI当其为低电平时编码器才能正常工作 还有两个输出端GS和E0用于扩展编码功能GS为0表示编码器处于工作状态 且至少有一个信号请求编码E0为0表示编码器处于工作状态 但没有信号请求编码。 74LS148芯片管脚:0-7 编码输入端(低电平有效) EI 选通输入端(低电平有效),A0、A1、A2 三位二进制编码输出信号即编码输出端(低电平有效),GS 片优先编码输出端即宽展端(低电平有效),EO 选通输出端,即使能输出端。 芯片管角使用方法: (1)0-7 EI 选通输入端(低电平有效) (2)编码输入端(低电平有效); (3)A0、A1、A2 三位二进制编码输出信号即编码输出端(低电平有效); (4)GS 片优先编码输出端即宽展端(低电平有效); (5)EO 选通输出端,即使能输出端; 3.设计思路 构建8-3线优先编码器的实验电路。输入信号通过单刀双掷开关接优先编码器的输入端开关通过键盘上的A至H键控制接高电平(VCC)或低电平(地)。使能端通过空格键控制接高电平或低电平。输出端接逻辑探测器的监测输出。 在本次优先编码器的设计规定优先级顺序,采用A—H之间代表输入,其中优先级别从A至H依次增高,进而H的优先级别最高。用指示灯显示输出,从