UART(中文版的数据手册)

第十一章异步串口通信

概述

S3C2410的UART提供3个独立的异步串行通信端口,每个端口可以基于中断或者DMA进行操作。换句话说,UART控制器可以在CPU和UART之间产生一个中断或者DMA请求来传输数据。UART在系统时钟下运行可支持高达230.4K 的波特率,如果使用外部设备提供的UEXTCLK,UART的速度还可以更高。每个UART通道各含有两个16位的接收和发送FIFO。

S3C2410的UART包括可编程的波特率,红外接收/发送,一个或两个停止位插入,5-8位数据宽度和奇偶校验。

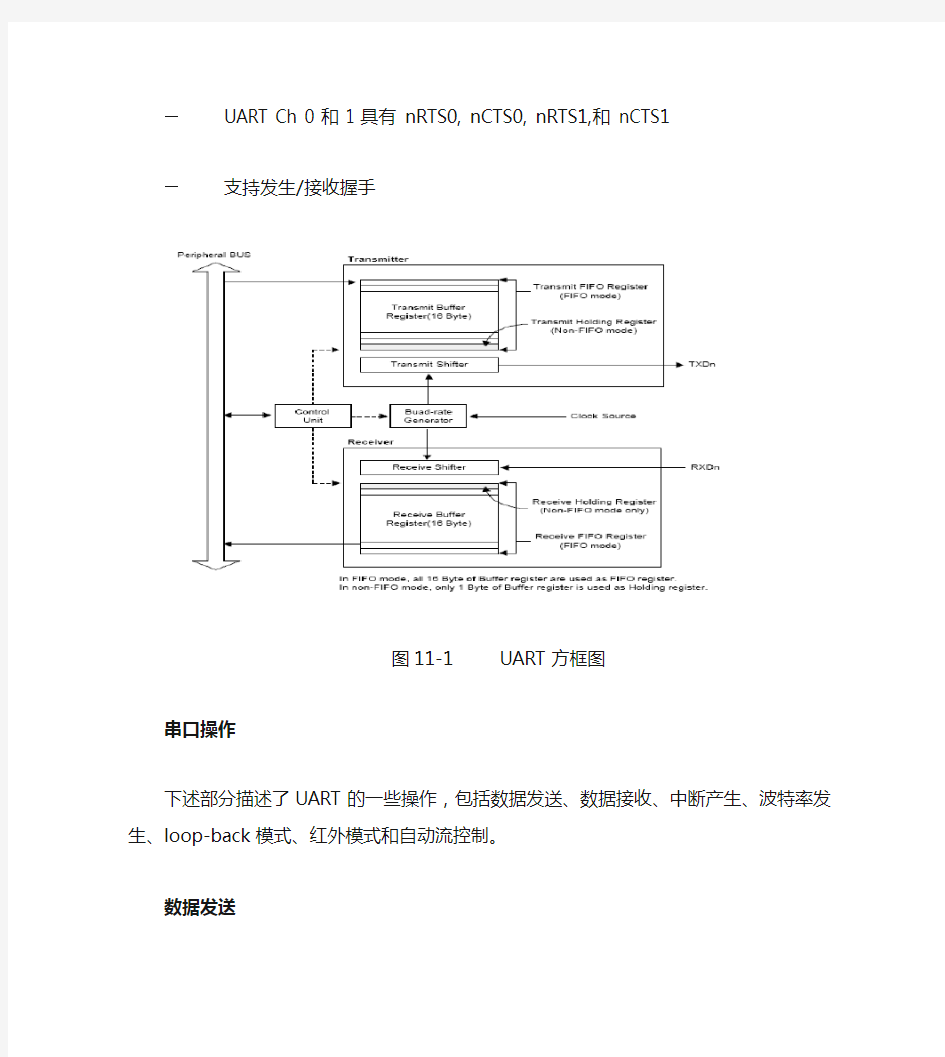

每个UART包括一个波特率发生器、一个发送器、一个接收器和一个控制单元,如图11-1所示。波特率发生器的输入可以是PCLK或者UEXTCLK。发送器和接收器包含16位的FIFO和移位寄存器,数据被送入FIFO,然后被复制到发送移位寄存器准备发送,然后数据按位从发送数据引脚TxDn输出。同时,接收数据从接收数据引脚RxDn按位移入接收移位寄存器,并复制到FIFO。

特性

—RxD0, TxD0, RxD1, TxD1, RxD2, 和TxD2基于中断或者DMA操作

—UART Ch 0, 1, 和 2 具有 IrDA 1.0 & 16 字节 FIFO

—UART Ch 0 和 1 具有 nRTS0, nCTS0, nRTS1, 和 nCTS1

—支持发生/接收握手

图11-1 UART方框图

串口操作

下述部分描述了UART的一些操作,包括数据发送、数据接收、中断产生、波特率发生、loop-back模式、红外模式和自动流控制。

数据发送

发送数据的帧结构是可编程的,它由1个起始位、5-8个数据位、1个可选的奇偶位和1-2个停止位组成,这些可以在线控制寄存器ULCONn中设定。接收器可以产生一个断点条件——使串行输出保持1帧发送时间的逻辑0状态。当前发送字被完全发送出去后,这个断点信号随后发送。断点信号发送之后,继续发送数据到Tx FIFO(如果没有FIFO则发送到Tx保持寄存器)。

数据接收

与数据发送一样,接收数据的帧格式也是可编程的。它由1个起始位、5-8个数据位、1个可选的奇偶位和1-2个停止位组成,这些可以在线控制寄存器ULCONn 中设定。接收器可以探测到溢出错误和帧错误。

—溢出错误:在旧数据被读出来之前新的数据覆盖了旧的数据

—帧错误:接收数据没有有效的停止位

当在3个字时间(与字长度位的设置有关)内没有接收到任何数据并且Rx FIFO非空时,将会产生一个接收超时条件。

自动流控制(AFC)

UART0和UART1通过nRTS and nCTS信号支持自动流控制,例如连接到外部UART时。如果用户希望将UART连接到一个MODEM,可以在UMCONn寄存器中禁止自动流控位,并且通过软件控制nRTS信号。

在AFC时, nRTS 由接收器的状态决定,而nCTS信号控制发送器的操作。只有当nCTS信号有效的时候(在AFC时,nCTS意味着其它UART的FIFO准备接收数据)UART发送器才会发送FIFO中的数据。在UART接收数据之前,当它的接收FIFO多于2字节的剩余空间时nRTS必须有效,当它的接收FIFO少于1字节的剩余空间时nRTS必须无效(nRTS意味着它自己的接收FIFO开始准备接收数据)。

图11-2 UART AFC接口

注:UART2不支持AFC功能,因为S3C2410没有nRTS2 和 nCTS2。

无AFC的例子

通过FIFO操作Rx

1、选择接收模式(中断还是DMA模式)。

2、检查UFSTATn寄存器中Rx FIFO的值。如果值小于15(RX FIFO 未满),用户必须将UMCONn[0]置1(nRTS生效),如果大于等于15(RX FIFO已满),用户必须将UMCONn[0]清0(nRTS无效)。

3、重复第2步。

通过FIFO操作Tx

1、选择发送模式(中断还是DMA模式)。

2、检查UMCONn[0]的值,如果为1(nRTS active),写数据到Tx FIFO

RS-232C接口

如果希望将UART连接到MODEM,nRTS, nCTS, nDSR, nDTR, DCD 和nRI信号是必须的。这种情况下用户可以通过GPIO控制这些信号因为AFC不支持RS-232C 接口。

中断/DMA请求的产生

每个UART有5个状态(Tx/Rx/Error)信号:溢出错误、帧错误、接收缓冲满、发送缓冲空和发送移位寄存器空。这些状态体现在UART状态寄存器中的相关位(UTRSTATn/UERSTATn)。

溢出错误和帧错误与接收错误状态相关,每个错误可以产生一个接收错误状态中断请求,如果控制寄存器UCONn中的receive-error-status-interrupt-enable位被置1的话。如果探测到一个receive-error-status-interrupt-enable位,通过读UERSTSTn的值可以识别这一中断请求。

控制寄存器UCONn的接收器模式为1(中断或者循环检测模式):当接收器在FIFO模式下将一个数据从接收移位寄存器写入FIFO时,如果接收到的数据到达了Rx FIFO的触发条件,Rx中断就产生了。在无FIFO模式下,每次接收器将数据从移位寄存器写入接收保持寄存器都将产生一个RX中断请求。

如果控制寄存器的接收和发送模式选择为DMAn请求模式,在上面的情况下则是DMAn请求发生而不是RX/Tx中断请求产生。

UART错误状态FIFO

UART除了Rx FIFO外还有错误状态FIFO。错误状态FIFO指示接收到的哪个数据有错误。只有当有错误的数据准备读出的时候才会产生错误中断。要清除错误状态FIFO,URXHn和UERSTATn必须被读出。

例如:假设UART Rx FIFO顺序接收到ABCD4个字符,在接收B的时候发生了帧错误。事实上UART接收错误并未产生任务错误中断,因为错误的数据B还没有被读出,只有当读B字符的时候才会发生错误中断。图11-3描述了这一例子。

波特率发生器

每个UART的波特率发生器提供串行时钟给接收器和发送器。波特率发生器的时钟源可以选择呢不系统时钟或者UEXTCLK。换句话说,通过设置UCONn的时钟选择被除数是可选的。波特率时钟通过对时钟源(PCLK OR UEXTCLK)进行16分频,然后进行一个16位的除数分频得到,这个分频数由波特率除数寄存器UBRDIVn指定。UBRDIVn可由下式得出:

UBRDIVn = (int)(PCLK/(bps * 16) ) -1

此除数应该在1-(2的16方-1)之间。

为了UART的精确性,S3C2410还支持UEXTCLK作为被除数。

如果使用UEXTCLK(由外部UART设备或者系统提供),串行时钟能够精确地和UEXTCLK同步,因此用户可以得到更精确的UART操作,UBRDIVn由下式决定:UBRDIVn = (int)(UEXTCLK / (bps x 16) ) –1

此除数应该在1-(2的16方-1)之间,且UEXTCLK要比PCLK低。

例如,如果波特率为115200bps,而PCLK或者UEXTCLK为40MHz,则UBRDIVn为:

UBRDIVn = (int)(40000000/(115200 x 16)) -1

= (int)(21.7) -1

= 21 -1 = 20

波特率错误容差

UART的帧错误应该少于1.87%(3/160)。

UART Frame error should be less than 1.87%(3/160).

tUPCLK = (UBRDIVn + 1) x 16 x 1Frame / PCLK tUPCLK : Real UART Clock tUEXACT = 1Frame / baud-rate tUEXACT : Ideal UART Clock UART error = (tUPCLK – tUEXACT) / tUEXACT x 100%

注意:1、1帧=起始位+数据位+奇偶位+停止位

2、在特定条件下,波特率上限可达921.6K,例如当PCLK为60MHZ时,可以使用921.6K的波特率而误差为1.69%

loop-back模式

为了识别通讯连接中的故障,UART提供了一种叫loop-back模式的测试模式。这种模式结构上使能了UART的TXD和RXD连接,因此发送数据被接收器通过RXD 接收。这一特性允许处理器检查每个SIO通道的内部发送到接收的数据路径。可以通过设置UART控制寄存器UCONn中的loopback位选择这一模式。

红外 (IR)模式

UART支持红外 (IR)接收和发送,可以通过设置UART线控制寄存器ULCONn的Infra-red-mode位来进入这一模式。图11-4阐述了如何实现IR模式。

在IR发送模式下,发送脉冲的比例是3/16——正常的发送比率(当发送数据位为0的时候);在IR接收模式下,接收器必须检测3/16的脉冲来识别0值(见图11-6和11-7所示的帧时序)。

UART SFR

UART线控制寄存器ULCONn

有3个UART线控制寄存器:ULCON0, ULCON1, and ULCON2

有3个UART控制寄存器:UCON0, UCON1, and UCON2

注意:DMA接收有FIFO模式下,当UART没有达到FIFO触发条件而且3个字时间没有接收到数据时,Rx中断会产生,用户应该检查FIFO的状态并读出其它数据。

UART FIFO控制寄存器UFCONn

波特率除数寄存器UBRDIVn

有3个波特率除数寄存器:UBRDIV0,UBRDIV1,UBRDIV2,存储于里面的值用于设置串口波特率:

UBRDIVn = (int)(PCLK / (bps x 16) ) –1

或UBRDIVn = (int)(UEXTCLK / (bps x 16) ) –1

此除数应该在1-(2的16方-1)之间,且UEXTCLK要比PCLK低。

例如,如果波特率为115200bps,而PCLK或者UEXTCLK为40MHz,则UBRDIVn为:

UBRDIVn = (int)(40000000/(115200 x 16)) -1

= (int)(21.7) -1

= 21 -1 = 20

TLV5638中文数据手册

TLV5638中文数据手册 By Hi_Cracker @whu 2.7-V至5.5 V低功耗双通道12位,具有内部参考电压 和掉电模式的数模转化器 Features: 双通道12位电压输出DAC 内部参考电压可编程 稳定时间可编程: 快速模式下1us 低速模式下3.5us 与TMS320和SPIE串行端口兼容 差分非线性度典型值<0.5 LSB 温度单调性 Applications 数字伺服控制回路 偏移和增益的数字调整 工业过程控制 机械和运动控制设备 大容量存储设备 Description TLV5638是一款双通道12位电压输出DAC,具有灵活的3线串行接口。串行接口允许与TMS320和SPIE,QSPIE,MicrowireE通信协议的串行端口进行无缝连接。它是通过16位串行字符串来完成编程的,其中包含4位控制字和12个数据位。 电阻串的输出电压经由增益为2的轨对轨输出缓冲器缓冲后输出。该缓冲器具有AB类输出级,因此,提高了稳定性并减少了建立时间。DAC建立时间的可编程,使设计师能够将速度与功耗进行最优化的处理。凭借其片上可编程的精密电压基准,TLV5638简化了整个系统的设计。 由于其源输出能力可高达1 mA,所以其片上参考电压也可以用来作为一个系统参考电压使用。采用CMOS工艺实现,该设备单电源工作,工作电压从2.7 V至5.5 V。它的封装形式是8-pin SOIC封装,在标准的商用,工业和汽车温度范围内的应用中,都大大减少了电路板空间。在军用温度范围内的应用中,它采用了JG 和FK封装。 Terminal Functions AGND:地 CS:芯片选通。数字输入低电平有效,用于使能/禁止输入。 DIN:串行数字输入。 OUTA:DAC A 通道模拟电压输出端 OUTB:DAC A 通道模拟电压输出端

MSP430FW427中文数据手册

MSP430xW42x混合信号微控制器 ●低电源电压范围:1.8V…3.6V ●超低功耗: -活动模式: 200 μA (1 MHz, 2.2 V) -等待模式:0.7 μA -关断模式(RAM保持):0.1 μA ●五种省电模式 ●6微秒内从等待状态唤醒 ●锁频环,FLL+ ●16位精简指令结构,125纳秒指令时间周期 ●应用于水、热和气体仪表的体积流量测量的SCAN-I/F单元 ●带有三个捕捉/比较寄存器的16位定时器Timer_A ●带有五个捕捉/比较寄存器的16位定时器Timer_A ●集成96段LCD驱动器 ●片内比较器 ●串行片上编程,无需外部编程电压,可编程的安全熔丝代码保护 ●FLASH器件具有程序装载器(BSL) ●系列成员包括: MSP430CW423: 8KB ROM存储器, 512B RAM MSP430CW425: 16KB ROM 存储器, 512B RAM MSP430CW427: 32KB ROM 存储器, 1KB RAM MSP430FW423: 8KB Flash存储器, 512B RAM MSP430FW425: 16KB Flash存储器, 512B RAM MSP430FW427: 32KB Flash存储器, 1KB RAM ●64引脚Quad Flat Pack(QFP)封装 ●完全的模块描述请参见: MSP430x4xx系列用户指南,文献号:SLAU056 说明 德州仪器公司的MSP430系列超低功耗微控制器由几个针对水、热和气体仪表等不同应用目标的片上系统(System-on-chip)具有不同外围设备的芯片系列组成。MSP430微控制器采用低功耗设计和16位精简指令结构,CPU内置16位寄存器以及常数发生器,能够实现最高的代码效率。锁频环FLL+和数控振荡器使得微处理器能在6微秒内从低功耗模式快速切换到工作模式。MSP430xW42x系列配置有两个内置16位定时器、一个比较器、一个SCAN接口模块、96段LCD驱动器和48个I/O引脚的微控制器。 MSP430的典型应用包括热量仪表、热水和冷水仪表、气体仪表和工业传感器系统。定时器支持额外的计数器应用、射频位流操作、IrDA和M-Bus通讯。

AD9959数据手册部分内容中文翻译

AD9959数据手册(部分) GENERAL DESCRIPTION概述 The AD9959 consists of four direct digital synthesizer (DDS) cores that provide independent frequency, phase, and amplitude control on each channel. This flexibility can be used to correct imbalances between signals due to analog processing, such as filtering, amplification, or PCB layout-related mismatches. Because all channels share a common system clock, they are inherently synchronized. Synchronization of multiple devices is supported. The AD9959 can perform up to a 16-level modulation of frequency, phase, or amplitude (FSK, PSK, ASK). Modulation is performed by applying data to the profile pins. In addition, the AD9959 also supports linear sweep of frequency, phase, or amplitude for applications such as radar and instrumentation. AD9959含有四个直接数字频率合成器(DDS),提供各通道独立的频率、相位和振幅控制。这种灵活性可以用来纠正信号之间的不平衡,这种不平衡是由于模拟处理,如滤波,放大,或PCB布局相关的不匹配导致。因为所有通道共用一个系统时钟,因此固有的同步。也支持多个设备的同步。AD9959可以执行16级频率、相位、振幅(FSK,PSK,ASK)调制,通过将数据传到配置引脚执行。此外,AD9959还支持频率、线性扫频、相位或振幅的应用,如雷达和仪表。 The AD9959 serial I/O port offers multiple configurations to provide significant flexibility. The serial I/O port offers an SPI- compatible mode of operation that is virtually identical to the SPI operation found in earlier Analog Devices, Inc., DDS products. Flexibility is provided by four data pins (SDIO_0/SDIO_1/ SDIO_2/SDIO_3) that allow four programmable modes of serial I/O operation. AD9959的串行I/O端口提供了多种配置,提供显著的灵活性。串行I / O端口提供了一个SPI兼容的操作模式,SPI操作与较早的模拟设备公司DDS产品几乎相同。灵活性是通过四个数据引脚(sdio_0 / sdio_1 /sdio_2 / sdio_3)允许四可编程串行I/O操作模式来实现的。 The AD9959 uses advanced DDS technology that provides low power dissipation with high performance. The device incorporates four integrated, high speed 10-bit DACs with excellent wideband and narrow-band SFDR. Each channel has a dedicated 32-bit frequency tuning word, 14 bits of phase offset, and a 10-bit output scale multiplier. AD9959采用先进的DDS技术,提供低高性能低功耗。该器件集成了四个高速10位DAC 具有优良的宽带和窄带SFDR。每个通道有一个专门的32位频率调谐字,14位相位偏移,和一个10位幅度调节输出。 The DAC outputs are supply referenced and must be terminated into AVDD by a resistor or an AVDD center-tapped transformer. Each DAC has its own programmable reference to enable different full-scale currents for each channel. The DDS acts as a high resolution frequency divider with the REFCLK as the input and the DAC providing the output. The REFCLK input source is common to all channels and can be driven directly or used in combination with an integrated REFCLK multiplier (PLL) up to a maximum of 500 MSPS. The PLL multiplication factor is programmable from 4 to 20, in integer steps. The REFCLK input also features an oscillator circuit to support an external crystal as the REFCLK source. The crystal must be between 20 MHz and 30 MHz. The crystal can be used in combination with the REFCLK multiplier.

中文数据手册

AD9854 特征 ·300M内部时钟频率 ·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作 ·正交的双通道12位D/A转换器 ·超高速比较器,3皮秒有效抖动偏差 ·外部动态特性: 80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A ·4倍到20倍可编程基准时钟乘法器 ·两个48位可编程频率寄存器 ·两个14位可编程相位补偿寄存器 ·12位振幅调制和可编程的通断整形键控功能 ·单引脚FSK和BPSK数据输入接口 ·PSK功能可由I/O接口实现 ·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能 ·具有过渡FSK功能 ·在时钟发生器模式下,有小于25 ps RMS抖动偏差 ·可自动进行双向频率扫描 ·能够对信号进行sin(x)/x校正 ·简易的控制接口: 可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电 ·具有多路低功耗功能 ·单输入或差分输入时钟 ·小型80脚LQFP 封装 应用 ·便携式频率特性分析仪 ·可编程时钟发生器 ·应用于雷达和扫频系统的脉冲调频信号源 ·测试和测量设备 ·商业和业余的射频(RF)发射机 概述 AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。输出17位相位截断保证了良好的无杂散动态范围指标。AD9854允许输出的信号频率高达150MHZ,而数字调制输出频率可达100MHZ。通过内部高速比较器正弦波转换为方波输出,可用作方便的时钟发生器。器件有两个14位相位寄存器和一个用作BPSK操作的引脚。对于高阶的PSK调制,可通过I/O接口改变相位控制字实现。具

TLV5618中文数据手册

TLV5618A 带掉电功能2.7V-5.5V低功耗双路12位数模转换器特点应用 ●双路12位电压输出DAC ●数字伺服控制回路 ●可编程调节转换时间●数字增益和增益调节 - 快速模式 3μs ●工业过程控制 - 低速模式 10μs ●机器和运动装置控制 ●兼容TMS320和SPI串行接口●大容量存储设备 ●典型微分非线性值<0.5LSB ●单调的温度 ●直接替换TLC5618A(C和I后缀) ●汽车类可用 汽车上的应用高可靠性 配置控制/打印支持 汽车行业标准 描述 TLV5618A是一个带灵活的3线串行接口 的双12位电压输出型的数模转换器。串行 接口兼容TMS320、SPI、QSPI和Microwire 串行接口。16位串行编程位包括4位控制和 12位数据位。 电阻串输出电压是由一个2倍增益的轨 到轨输出缓冲器。缓冲区具有AB类输出级, 以提高稳定性和减少建立时间。可编程DAC 的转换时间以允许设计师优化速度与功耗。 CMOS工艺制作,该设备支持2.7V-5.5V单一电源。它可在标准的商业和工业温度范围内的8引脚SOIC封装。 TLV5618AC可工作温度范围为0℃到70℃,TLV5618AI可工作温度范围为-40℃到85℃,TLV5618AQ可工作温度范围为-40℃到125℃,TLV5618AM可工作温度范围为-55℃到125℃。 请注意,有关可用性,标准保修一个重要的通知,和使用的关键应用德州仪器产品和免责条款出现在此数据手册的末尾。 SPI和QSPI是摩托罗拉公司注册商标。

TLV5618A 带掉电功能2.7V-5.5V低功耗双路12位数模转换器功能框图

dac904数据手册中文版

14位,165M SPA(采样率) DAC(数模转换器) 特性: ●单电源供电+5V或+3V ●高SFDR (无杂散动态范围):在100MSPS 64dBc时20MHz输出 ●低干扰:3PV -S ●低功耗:170MW (+5 V时) 应用 ●通讯传输通道 WLL ,蜂窝基站 数字微波链路 电缆调制解调器 ●波形产生 直接数字频率合成器(DDS ) 任意波形发生器(ARB ) ●医疗/超声 ●高速仪表和控制 ●视频,数字电视 说明: DAC904是一款高速数模转换器,14位分辨率,引脚兼容DAC908、DAC900、DAC902,分别提供8-,10-,12-位分辨率选择。该系列DAC支持的所有型号更新率超过165MSPS,具有优良的动态性能。 DAC904先进分割架构的优化为单音和多频音信号提供高无杂散动态范围(SFDR),尤其是用于通信系统的发送信号电路时。 DAC904具有高阻抗(200KΩ)的电流输出,标称范围为20mA和一个最多为1.25V的输出。差分输出允许两个差分或单端模拟信号的接口。电流输出的匹配确保在差分结构中出色的动态性能,它可以与变压器配合使用。 利用一个小的几何CMOS工艺,单片DAC904可以用在+2.7 V至+5.5 V宽的单电源范围内操作。其低功耗特性允许它使用在便携式和电池供电系统情况下。可通过降低输出电流与调整满量程选项实现进一步优化。 DAC904不断运转时,掉电模式导致其待机功率仅为为45mW 。 DAC904带有一个集成的1.24V带隙基准和边沿触发输入锁存器,提供完整的转换器解决方案。+3 V和+5 V CMOS逻辑系列都可以接口到DAC904 。 DAC904的参考结构允许使用芯片上的参考,或施加外部参考。通过一个外部电阻,满量程输出电流可以调整在2 - 20mA,并保持其指定的动态性能。

dac902中文简介

特征 q 单+5V或+3V操作 q HIGH SFDR:在5MHz 100MSPS: 67dBc输出 q 低干扰:3pV-s q 低功耗:在170mW +5V q 内部参考: 可选的分机.参考 可调全量程范围 乘法选项 应用 q 通讯发送通道: WLL, 蜂巢式基站 数字微波链路 电缆调制解调器 q 波形产生: 直接数字频率合成器(DDS) 任意波形产生(ARB) q 医学/超声 q 高速仪表和 控制 q 视频,数字TV 描述 该DAC902是一种高速,digital-to-analog转换(DAC)提供力所能及的一12-bit 分解选项Speed Plus 系列高性能转换器.具有引脚兼容性在系列成员,DAC908, DAC900,和DAC904提供元件选择选项为8-, 10-,和14-bit分解分别.在此的D / A 系列所有机型转换器支持在165MSPS过剩与更新率出色的动态性能,特别适合满足多种应用的需求.该DAC902先进分割架构优化,以提供高无杂散动态范围(SFDR)单色调,以及多音信号,必要时,对通信信号传输路径中使用-tion系统.该DAC902具有较高的电流输出阻抗(200k?)一个20mA标称范围,输出符合最多1.25V.的差动输出端允许既是一个差分或单端模拟信号接口.紧密匹配的电流输出确保出色的动力性能差分配置,可与实施变压器.利用一小几何CMOS过程中,单片DAC902可以运作,宽,单电源范围+2.7V到+5.5V.其低功耗在允许使用便携式和电池供电系统.可以进一步优化通过降低实现的可调输出电流全面的选择 对于在DAC902,掉电不连续操作

在待机功率只有45mW模式的结果.该DAC902具有集成1.24V带隙来参考,ence和边沿触发输入锁存器,提供一个完整的转换器解决方案.双方+3V和+5V CMOS逻辑家庭可以连接到DAC902.该DAC902参考结构允许额外 利用灵活的片上参考或应用一外部参考.满量程输出电流可以调整在一段2mA跨度20mA,一个外部电阻器,而保持指定的动态性能.该DAC902在SO-28和TSSOP-28包可供 应用信息 操作原理 该DAC902 uses架构的电流导引技术来实现快速开关和高更新率.内的单片D核心元素/ A转换器是一个数组分段电流源,其目的是为了提供全面的输出电流可达20mA(见图1).内部解码器的地址差电流开关每次更新和DAC相应的输出电流是由督导所有要么输出电流总结波节,I OUT or I OUT .互补输出提供一个差分输出信号,从而提高了动态性能测试减少偶次谐波,共模信号(噪声),双输出信号的peak-to-peak摇摆两个因素,相较于单端工作.分割结构的结果会有很大的红眼,在干扰能源tion,提高了动态perfor -曼斯(SFDR),和DNL.的电流输出保持非常高的更大的输出阻抗比200k?.满量程输出电流的比例确定内部基准电压和外部(1.24V)电阻,R SET.由此产生的I REF内部乘以一个32因素产生一个有效DAC输出电流这可以从2mA到20mA,的价值而定对R SET.该DAC902分为数字和模拟部分,每一个是通过自身的供电电源引脚.该数字部分包括边沿触发的输入锁存器和解码器的逻辑,而模拟部分包括电流租金及其相关交换机的源数组, 参考电路. DAC传递函数

A3955中文数据手册

A3955步进电机驱动专用集成芯片 驱动电路采用使用A3955步进电机驱动专用集成芯片,通过使用该芯片可以完成电机的恒流集成驱动,恒转矩控制,并且实现电流检测与保护功能。 A3955SB和A3955SLB是为驱动双极型步进电机在微步工作模式下的一相绕组而设计的。该芯片可以输出±1.5V之间的电流和50V以内的电压。内部脉宽调制模块以及3位非线性数模转换器使得电机电流可以控制在整步,1/2,1/4,1/8微步模式。 非线性增量减少了微步控制线的数量。微步能够增加电机的运行步数,减小了转矩变化以及电机在低速运行时的共振问题。 内部电路决定了脉宽调制电流控制电路是工作在慢电流衰减模式,快电流衰减模式还是混合电流衰减模式下。芯片在这三中工作模式下,驱动管关断时间均被分成一段时间的快速电流衰减,以及剩下时间的慢速电流衰减。 用户选择的电流检测电阻和参考电压值两者共同决定了输出电流比率;慢速,快速或者混合电流衰减模式给用户提供了广阔变化的电机控制的选择范围。 内部保护电路包括带滞回的过热关断电路,暂态抑制二极管,以及交叉流保护电路。无特殊的上电次序要求。 A3955芯片特点: (1)±1.5A连续输出电流 (2)50V输出电压范围 (3)内部脉宽调制电流控制 (4)3位非线性数模转换器 (5)快速,混合,和慢速三种电流衰减模式 (6)芯片内部有瞬态抑制二极管 (7)芯片内部有过热关断电路 (8)交叉电流及低压关断保护电路 (9)表4-4 A3955模数转换真值表

图4-4 A3955驱动芯片引脚图表4-5引脚功能表

图 4-5 A3955驱动芯片结构框图

DAC7565中文简明手册

DAC7565中文简明手册 12位,四通道,低脉冲干扰,电压输出,2.5V内部参考电压模数转换器 特性: 相对精度:0.5LSB 故障能量:0.15nV-s 内部参考电压:2.5V默认;初始精度0.004%;温漂2-5ppm/Oc;20mA源能力; 上电复位到0标度或中间标度; 异步清除到0标度或中间标度; 超低功耗1mA (5V时) 宽电压范围2.7-5.5V 温度范围内12位单调 稳定时间10uS到±0.024%全范围 低功耗串行口带施密特输入最高50MHz 片内输出缓冲放大器,带轨到轨操作 1.8-5.5V逻辑兼容 温度范围-40到+105度 应用范围: 便携式仪器;闭环伺服控制;过程控制PLC;数据采集系统;可编程衰减;电脑外设。相关器件 16-BIT 14-BIT 12-BIT 引脚功能兼容DAC8565 DAC8165 DAC7565 功能兼容DAC8564 DAC8164 DAC7564 描述: DAC7565是低功耗,电压输出、四通道12位数模转换器。该设备包括一个2.5 v内部参考电压(默认启用),给2.5 v的全范围输出电压。内部参考的初始精度0.02%,可以在VREFH/ VREFOUT引脚提供20mA电路。该设备是单调的,提供了很好的线性,和最小码到码瞬态干扰电压(故障)。DAC7565使用多功能3-wire串行接口最高50 mhz的时钟频率。接口是兼容标准SPI QSPI, Microwire,和数字信号处理器的接口。 DAC7565包含上电复位电路,保证了DAC输出电压在0档或中档,直到一个有效的代码写入设备。该设备包含一个省电功能,通过串行接口,减少设备的电流1.3μa在 5 v时。功耗在3 v 时2.9 mw, 省电模式减少到1.5μw。内部参考,低功耗和小封装让这个设备适合便携式电池供电设备。 DAC7565 向下引脚兼容和功能兼容DAC8165 DAC8565,和功能兼容DAC7564 DAC8164 DAC8564。所有这些设备都是TSSOP-16封装。

stm32f407数据手册中文

1,参考资料 1. Stm32f4数据手册:stm32f407zgt6.pdf 2. Stm32f4中文手册:stm32f4xx中文参考手册.pdf 3.开发板原理图:Explorer stm32f4_ Vxx_ SCH.pdf 2,芯片内部资源 1.芯片图片 2.芯片参数表 3.内核 (1)32位高性能Arm Cortex-M4处理器 (2)时钟:高达168MHz,实际上可以稍微超频一点(3)支持FPU(浮点运算)和DSP指令 4. IO端口 (1)Stm32f407zgt6:144针114 IO端口

(2)大多数IO端口可以承受5V(模拟通道除外) (3)支持调试:SWD和JTAG,SWD只需要2条数据线 5.记忆 (1)内存容量:1024k闪存,192K SRAM 6.时钟,复位和电源管理 (1)1.8?3.6V电源和IO电压 (2)上电复位和可编程掉电监控 (3)强大的时钟系统 -4?26m外部高速晶体振荡器 内部16 MHz高速RC振荡器 -内部锁相环(PLL,倍频),PLL倍频后,一般系统时钟是外部或内部高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源 7.低功耗

(1)三种低功耗模式:睡眠,停止和待机 (2)RTC和备用寄存器可以由电池供电 8,广告 (1)3个12位AD [最多24个外部测试通道] (2)内部通道可用于内部温度测量 (3)内置参考电压 9,DA (1)两个12位Da 10,DMA (1)16个具有FIFO和突发支持的DMA通道 (2)支持的外设:定时器,ADC,DAC,SDIO,I2S,SPI,I2C和USART 11.多达17个计时器 (1)10个通用计时器(TIM2和tim5为32位)

PCF8591中文手册

PCF8591 8位A/D和D/A转换器

1、特性 z单电源供电 z工作电压:2.5 V ~ 6 V z待机电流低 z I2C总线串行输入/输出 z通过3个硬件地址引脚编址 z采样速率取决于I2C总线速度 z4个模拟输入可编程为单端或差分输入 z自动增量通道选择 z模拟电压范围:VSS~VDD z片上跟踪与保持电路 z8位逐次逼近式A/D转换 z带一个模拟输出的乘法DAC 2、应用 z闭环控制系统 z用于远程数据采集的低功耗转换器 z电池供电设备 z在汽车、音响和TV应用方面的模拟数据采集 3、概述 PCF8591是单片、单电源低功耗8位CMOS数据采集器件,具有4个模拟输入、一个输出和一个串行I2C总线接口。3个地址引脚A0、A1和A2用于编程硬件地址,允许将最多8个器件连接至I2C 总线而不需要额外硬件。器件的地址、控制和数据通过两线双向I2C总线传输。 器件功能包括多路复用模拟输入、片上跟踪和保持功能、8位模数转换和8位数模拟转换。最大转换速率取决于I2C总线的最高速率。 4、订货信息

5、内部框图 图1 内部框图 6、引脚 图2 引脚图 (DIP16).

7、功能描述 7.1 地址 I2C总线系统中的每一片PCF8591通过发送有效地址到该器件来激活。该地址包括固定部分和可编程部分。可编程部分必须根据地址引脚A0、A1和A2来设置。在I2C总线协议中地址必须是起始条件后作为第一个字节发送。地址字节的最后一位是用于设置以后数据传输方向的读/写位。(见图4、16、17) 图4 地址 7.2 控制字 发送到PCF8591的第二个字节将被存储在控制寄存器,用于控制器件功能。控制寄存器的高半字节用于允许模拟输出,和将模拟输入编程为单端或差分输入。低半字节选择一个由高半字节定义的模拟输入通道(见图5)。如果自动增量(auto-increment)标志置1,每次A/D转换后通道号将自动增加。 如果自动增量(auto-increment)模式是使用内部振荡器的应用中所需要的,那么控制字中模拟输出允许标志应置1。这要求内部振荡器持续运行,因此要防止振荡器启动延时的转换错误结果。模拟输出允许标志可以在其他时候复位以减少静态功耗。 选择一个不存在的输入通道将导致分配最高可用的通道号。所以,如果自动增量(auto-increment)被置1,下一个被选择的通道将总是通道0。两个半字节的最高有效位(即bit 7和bit 3)是留给未来的功能,必须设置为逻辑0。控制寄存器的所有位在上电复位后被复位为逻辑0。D/A转换器和振荡器在节能时被禁止。模拟输出被切换到高阻态。

DAC7564中文简明使用手册

12位4通道极低功耗电压输出内置2.5V 2ppm/℃参考的数模转换器 特性 ●相对精度:0.5LSB ●内置2.5V参考电压 ●上电自动复位到0 ●低功耗:5V供电时电流1mA ●宽电压范围:+2.7V—+5.5V 简述 DAC7564是一个低电耗、电压输出、4通道、12位数模转换器。该芯片内置2.5V,2ppm/℃的参考电压,输出电压最大为2.5V。该芯片具有良好的线性。DAC7564使用一个3线串行接口,该接口的时钟可以高达50MHz。 DAC7564包含上电复位电路,确保DAC上电后输出0并且一直保持直至有效数值写入。 引脚说明 引脚说明

串行口写操作时序

操作原理数模转换部分(DAC)

芯片DAC部分如图, 当DAC7564输入码为二进制,电压输出用以下公式计算: 式中DIN=装入DAC寄存器的二进制数的等效十进制数,它的取值范围是0—4095;X代表通道A、B、C、D。 内部参考电压 DAC7564芯片包含一个2.5V的内置参考电压,芯片的缺省状态使用该电压。内部参考电压可以在VrefH/VrefOUT脚输出,我们推荐在VrefH/VrefOUT 引脚和GND之间接入一个100nF的电容滤除噪声。 使用/不使用内部参考电压 DAC7564的内部参考电压缺省状态下自动使用,然而,您也可以不使用该参考电压,而使用外接的参考电压。我们可以从串行口输入一个24位的命令,芯片将改变缺省设置。这里不深入研究。 串行接口 DAC7564有一个3线串行接口(SYNC,SCLK和DIN),与SPI,QSPI等标准匹配。

DAC7564的输入移位寄存器是24位的,DB23-DB16是8个控制位,DB15—DB4是12个数据位,DB0—DB3是4个无关位,可以忽略。所有的24位数据在时钟脉冲SCLK的控制下进入寄存器。DB23最先装入。DAC7564收到所有的24位数据解码前8位决定DAC的操作/控制模式。接下来的12位数据决定模拟量输出。数据格式是:全0对应0V,全1对应满量程(Vref-1LSB),也就是0FFFH对应满量程。 写时序从SYNC线变成低电平开始,DIN口的数据在SCLK的每个下跳沿逐位进入24位移位寄存器。串行时钟的频率最高可达50MHz。在串行时钟的第24个下跳沿,最后的数据位进入移位寄存器,移位寄存器锁定。再有时钟脉冲也不会改变移位寄存器的内容。当24位数据被锁存入移位寄存器后,高8位用作控制位,接下来的12位为数据位。串行时钟的第24个下跳沿后,DAC7564将解码并完成相应的操作,而不必等待SYNC的上升沿。新的写入时序需要SYNC的下一个下跳沿。如果在第24个下跳沿之前,SYNC的电平上升为高电平,本次操作将中断,但不会影响输出。 IOVdd和电压变换 IOVdd引脚给DAC7564的数字部分供电。对于单电源系统,可以把它和A Vdd接在一起。对于双电源系统,数字逻辑部分使用IOVdd供电,而模拟部分使用A Vdd供电。 输入移位寄存器 DAC7564支持几条命令:(只介绍最常用几条) DB21=0 DB20=0:单通道存储命令 对应一个DB18和DB17选择的DAC对应的移位寄存器的内容被更新。也就是说,只更新某一个移位寄存的内容,该移位寄存器具体和哪一个DAC通道对应,根据DB18和DB17的内容确定。 DB21=0 DB20=1:单通道更新命令 一个DAC通道的移位寄存器和内容和DAC寄存器的内容同时被更新。 DB21=1 DB20=0:同时更新 一个通道的移位寄存器内容更新,所有DAC输出通道同时更新。 LDAC功能 DAC7564有两个更新:软件更新和硬件更新。DAC的双缓冲使得新的的数据被送入芯片而不会干扰模拟量输出。 DAC7564的数据在第24个下跳沿同步更新,对于这种同步更新,LDAC引脚直接接地而不需专门关注。如果要使用LDAC引脚功能,应该使用单通道

stm32f407数据手册中文

1参考资料 1Stm32f4数据手册:stm32f407zgt6.pdf 2Stm32f4中文手册:stm32f4xx中文参考手册.pdf 三。开发板原理图:Explorer stm32f4_Vxx_附件pdf 2芯片内部资源 1芯片图片 2芯片参数表 三。内核 (1)32位高性能Arm Cortex-M4处理器 (2)时钟:高达168MHz,实际上可以稍微超频(3)支持FPU(浮点运算)和DSP指令 4IO端口 (1)Stm32f407zgt6:144针114 IO端口

(2)大多数IO端口可以承受5V(模拟通道除外) (3)支持调试:SWD和JTAG,SWD只需要2条数据线 5记忆 (1)内存容量:1024k闪存,192K SRAM 6时钟、复位和电源管理 (1)1.8~3.6V电源及IO电压 (2)上电复位和可编程断电监控 (3)强大的时钟系统 -4~26m外接高速晶体振荡器 内置16MHz高速RC振荡器 -内部锁相环(PLL,倍频),经过PLL乘法后,一般的系统时钟是外部或内部的高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源 7低功耗

(1)三种低功耗模式:休眠、停止和待机 (2)RTC和备用寄存器可由电池供电 8广告 (1)3个12位AD[最多24个外部测试通道] (2)内部通道可用于内部温度测量 (3)内置参考电压 9,达卡 (1)两个12位Da 10DMA系统 (1)16个DMA信道,支持FIFO和突发 (2)支持的外围设备:定时器、ADC、DAC、SDIO、I2S、SPI、I2C和USART 11最多17个计时器 (1)10个通用定时器(TIM2和tim5为32位)

AD9851中文数据手册

AD9851中文数据手册 By Hi_Cracker @whu CMOS180 MHzDDS / DA (合 成器 AD9851 FEATURES 32bit 频 率 便捷的编辑控制接口:并行或串行 异步加载格式 5位相位调制和偏置功能 比较器抖动<80 ps 的P-P 在20兆赫 2.7 V 至5.25 V 单电源供电 低功耗:555毫瓦@180 MHz 掉电功能:4 mW@2.7 V 超小28引脚SSOP 封装 应用: 频率/相位灵活可变的正弦波合成 数字时钟恢复和锁定电路 通信领域 数控ADC 编码发生器 通信领域中灵活地本地振荡器 正交振荡器 CW ,AM ,FM ,FSK MSK 调制发射机 GENERAL DESCR IP TION AD9851是一个高度集成的器件,采用先进的 性能D / A 转换器,比较器,实现了一个数字可 编程频率合成器和时钟发生器 的功能。引入一个精确的时钟源, AD9851可以产生 一个稳定的, 频率和相位 可编程的正弦波。此正弦波可以直接用作频率源或在内部 转化为方波,然后 作为灵活的时钟发生器使用。 AD9851的创新型高速 DDS 内核可 以接受一个 32位频率控制字,从而可以产生一个最大 180 MHz 的输出时钟,其分辨率约 0.04Hz 。AD9851包含一个独特的6 * REFCLK 乘法器电路,不再需要一个高速 参 考振荡器。6 * REFCLK 乘法器对SFDR 和相位噪声的影响微乎其微。 AD9851 180 MHz 的时钟速率可选 6*参考时钟 片上高性能10位DAC 和高速滞回比较器 无杂散动态范围(SFDR > 43分贝@70 MHzAout 。 控 DDS 技术,结合内部高速,高

相关文档

- DAC0832中文手册

- DAC904E中文资料

- ES6629中文资料(List Unclassifed)中文数据手册「EasyDatasheet - 矽搜」

- MCP3208CN中文权威手册

- Nordic中文选型手册

- DAC7565中文简明手册

- DAC7564中文简明使用手册

- 中文数据手册

- AD9912纯中文数据手册

- dac0832中文资料_数据手册_参数

- stm32f407数据手册中文

- MSP430FW427中文数据手册

- AD9851中文数据手册

- cs42l52中文数据手册

- dac904数据手册中文版

- PCF8591中文资料_数据手册_参数

- PCF8591中文手册

- AD9959数据手册部分内容中文翻译

- DAC908UG4中文资料

- DAC904布线方法